by Kiichi Sakamoto, Advantest Corp., and Aki Fujimura, D2S Inc.

Executive overview

E-beam direct write (EbDW) lithography using character projection (CP) capability has the potential to enable maskless production for systems-on-chip (SoCs) at leading-edge technology nodes. Design for e-beam (DFEB) is an effective way to improve the throughput of CP machines by the order of magnitude needed to realize this potential. This paper presents a design and manufacturing collaboration between D2S and Advantest that yielded a 4× increase in the number of characters available on EbDW stencil masks, a key factor in achieving the throughput increase needed to make maskless SoCs practical for leading-edge nodes, and to eliminate mask cost as a barrier to innovation.

Maskless CP EbDW production, enabled by DFEB, eliminates mask costs for critical mask layers. Both the cost and time-to-market benefits of this approach are attractive for low-volume applications, or for applications with uncertain near-term volumes.

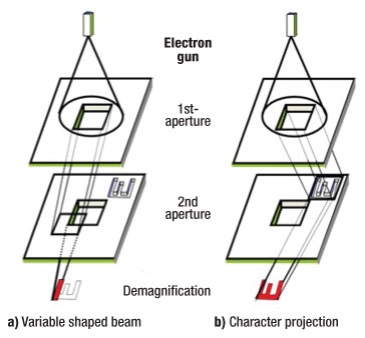

The traditional, variable-shaped beam (VSB) method of e-beam writing fractures the desired shape into constituent rectangles and sometimes 45° triangles. Thus, with VSB, writing a single character might require several exposures, or shots. CP, in contrast, uses stencils to deploy more complex characters on the second aperture of the e-beam machine in a single shot (Figure 1).

|

| Figure 1. VSB vs. CP. (Source: Hitachi High-Technologies Corp.) |

Since EbDW write times are almost linearly correlated with shot count, shot count determines the feasibility of maskless SoCs. To speed EbDW throughput enough to make maskless SoCs practical, shot count must be reduced by an order of magnitude. The shot count reduction achieved from CP depends on how many VSB shots are required to create a given design feature. SRAM core cells, for example, can require over 100 VSB shots, so a 100:1 reduction in shot count is possible with CP.

Each EbDW machine has a different number of CP characters available per stencil. The number of characters is critical, since any shapes on the wafer not represented by a character on the stencil mask must be shot with VSB. Previously, the Advantest F3000 EbDW machine specified a stencil mask containing 12 character block areas, each with 100 characters. This paper introduces a new, enhanced specification containing 20 character block areas, each with 220-280 characters, enabled by Packed Stencil technology from D2S.

Packed stencil

During EbDW lithography, the stencil mask is physically moved to position a certain character block area in the second aperture of the machine. Typically, the set of characters for any given layer of wafer processing are provided in one character block area, because physical movements of the stencil are time consuming.

The EbDW machine uses electrostatic deflection to switch almost instantaneously between characters within a character block area. To maintain accuracy, only a certain radius of e-beam deflection is allowed, limiting the number of characters that can be included in a character block area. The deflection radius, however, is not what has dictated the standard 12 character blocks, with 100 characters each. This limitation is actually the result of a disconnect between design and manufacturing.

Traditionally, a designer is not aware of what cells or layouts are easier or faster for an EbDW machine to shoot, so the machine must be ready to project literally any character. Thus, the standard stencil mask is laid out in a grid pattern with pre-designated spots for characters. Each character can be of any size or shape up to the maximum allowed size, which is dictated by the first aperture. In the case of the Advantest F3000 for 65nm, the maximum size is 4m by 4μm.

The critical layers with the most expensive and time-consuming mask overhead (diffusion, active, contact, metal 1, via 1, metal 2, etc.) predominately consist of standard cells and memory. These design features represent a finite set of characters that can be pre-determined and ready on a stencil mask for use on any design employing a given library. Additionally, with pre-determined characters, a grid to accommodate any character is unnecessary — characters can be arranged on the stencil to optimize the number of characters per block. The resulting new stencil technology is possible only through a design and manufacturing collaboration.

DFEB is the bridge between design and manufacturing that makes optimal use of stencil masks possible. A stencil mask layout, including all the characters needed to represent a given standard-cell library, is co-designed with a DFEB overlay library that designers use during physical design implementation to optimize their designs for EbDW shot count. This allows more patterns on the wafer to be shot as characters, reducing write times and lithography cost.

During co-design of the overlay library and stencil mask, the new stencil technology leverages the Advantest machine’s new capability to shoot from Packed Stencils to optimize the stencil mask layout for the number of characters per block. The new stencil technology does not change the total area used by characters in any given character block, so the characters are projected with no loss of accuracy.

As detailed below, 20 character block areas are more than sufficient for a given standard cell library. The F3000 also contains a stencil storage cassette holding up to five stencils, ready to use for multiple cell libraries without breaking vacuum.

DFEB overlay library

The majority of the shot-count reduction from CP and DFEB comes from standard cells and SRAMs. A typical standard cell library may have 600 to over 1000 standard cells, with four to 20 SRAM types. Using the DFEB methodology, a subset of the most usable and/or highest shot-count cells in a standard cell library is chosen to have a DFEB overlay library counterpart. Every cell in this subset will have a corresponding character on the stencil mask.

E-beam machines cannot "mirror" characters, so every orientation of a cell requires a different character, unless there is symmetry to exploit. To optimize the number of cells represented on the stencil, DFEB methodology limits the orientations available. Of the eight orientations possible, DFEB typically deploys two: a north-south, or "normal," orientation, and a "flipped south" (flipped on the X-axis) orientation.

Given two orientations of each cell, with the traditional 100 characters in a character block area, only about 50 different cells can be turned into characters for CP. The rest have to be shot with VSB. At first, the SRAM cores and the "top 40" standard cells that can be covered with 100-character stencils may seem sufficient. But, the potential order-of-magnitude improvement in shot count offered by CP and DFEB can only be achieved if more than 100 characters are available.

SRAM cores are the design elements densest in shot count, and typically are axis-symmetric. So, stencil characters for just the SRAM cores would seem to reduce shot count sufficiently. But, areas outside the core can account for as much as 20%-30% of the shots for an SRAM macro. This percentage is even higher for the smaller SRAM macros numerous in many of today’s designs. Even if SRAM cores required zero shots, the best shot-count reduction possible for an SRAM macro without characters for outside the core area is 3-5× — far less than the order of magnitude needed. So, shooting the periphery (sense amps, etc.) of the SRAMs with CP is critical to overall shot-count reduction.

Any DFEB design can be synthesized so that the top 30 or 40 standard cells represent an overwhelming majority of the shapes in the standard cell areas. With the "flipped-south" orientation, the total would be 60-80 characters. DFEB explicitly synthesizes the design with mostly logic cells that can be shot with CP. Since logic synthesis often chooses between many arbitrary options that are all equally good for area, power, and timing considerations, teaching synthesis tools to prefer one-shot CP cells in those situations doesn’t hurt the quality of the design. So, for any one particular design, 100 characters per character block area may be nearly sufficient.

However, the turn-around time advantage of going direct to silicon offered by DFEB depends on a design-independent stencil mask waiting in the EbDW machine for all designs that use a particular standard cell library. This requires more than 100 characters.

Fortunately, for the 65nm or 45nm technology nodes, standard cell libraries have a height significantly lower than 4μm, and the widths of some of the cells are not nearly the 4μm allowed in one character for the 100-character stencil. As a result, on Packed Stencils, characters can be grouped tightly, yielding, depending on layer and on standard cell libraries, to about 250 characters for the 65-45nm nodes.

Character sharing

To represent as many standard cells from a given library as possible on a stencil mask, in addition to increasing the number of characters per character block area from 100 to about 250, many of the 250 characters are designed to be shared by multiple standard cells in the DFEB overlay library.

An example of this character sharing is how output-drive variations of a cell can be handled using the partial CP (PCP) capability on EbDW machines. Just as the overlapping of squares on the first and second apertures produces rectangular VSB shots on EbDW machines, an overlapping of the square first aperture with a character in the second aperture can produce partially projected characters, or PCPs.

In a standard cell library, many of the basic cells used have multiple drive capabilities. For example, a buffer cell may have a 1/4X, 1/2X, 1X, 2X, 4X, 8X, and a 16X drive output variation. Typically, these are different standard cells. The layouts for these cells may or may not have shared components. Standard-cell layout designed for mask-based manufacturing has no incentive to share layout components for these buffer cells. For DFEB, there is a large incentive to have a single character represent as many standard cells as possible.

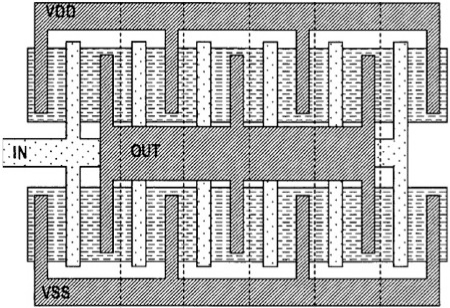

Figure 2 shows the layout of a cell’s output buffer section designed for e-beam using PCP. The diffusion, poly, metal and contact layers each would have a character that is used by the 1X, 2X, 3X…6X buffer versions of the same logic function. By "cutting" the character by the first aperture deflection at various positions indicated by the dotted vertical lines, different-sized buffers can be shot from the same characters. In this case, one character shoots six different standard cells.

|

| Figure 2. Multiple buffer cell using PCP. |

There is a high correlation between the most-used library cells, and library cells with multiple buffer size variations. As a result, even after taking "flipped south" orientations into account, with only about 250 characters in the character block area, over 130 standard cells in a given library, in addition to SRAM and other characters, can be shot by CP (or PCP).

Impact on design quality

With 130 standard cells in the DFEB overlay library, most designs can be synthesized to use predominantly the overlay library cells rather than cells from the original standard-cell library, which are shot using VSB. DFEB-driven synthesis would insist on using a cell from the original library only if needed for performance, power or area optimization. With 130 cells available, instead of 30 or 40, a design can be optimized for shot count without sacrificing other quality-of-result metrics.

Increasing the number of "one shot" CP cells in the DFEB overlay library also enables a wider variety of design types to achieve the order-of-magnitude shot count reduction needed to make EbDW practical for all critical layers of an SoC design.

Conclusion

EbDW has the potential to take all critical layers of an SoC design direct to silicon without incurring the costs and time-to-market delays of traditional mask production. However, for this to be practical, the shot count for standard cell designs must be reduced by an order of magnitude. To achieve this, the number of library and memory elements represented by "one-shot" CP characters on the stencil mask used by EbDW machines must be increased.

A deep collaboraton of design and manufacturing between Advantest and D2S has made the new stencil technology a reality. With these stencils, combined with the DFEB methodology, an order-of-magnitude decrease in shot count for the critical layers is achieved. This improved EbDW throughput enables maskless SoCs for leading-edge nodes, eliminating mask cost as a barrier. The resulting increase in design starts is good for the entire semiconductor supply chain.

Biographies

Kiichi Sakamoto received his BS degree in physics from St. Paul U., Japan, and is general manager of nanotechnology 1st business division at Advantest Corp., 1-5 Shin-tone, Otone-machi, Kitasaitama-gun Saitama 349-1158, Japan; ph.:+81 (480) 72-6300; e-mail [email protected].

Aki Fujimura received his BS/MS degrees in electrical engineering from MIT and is chairman and CEO of D2S Inc., 4040 Moorpark Avenue, San Jose, CA 95117; ph.: (408) 528-5990; e-mail [email protected].