March 17, 2010 – Among key takeaways from SEMATECH’s Litho Forum last week in New York City was a proposal to create a consortium to support multibeam mask writing efforts, similar to what’s being done for EUV.

A maskless and multibeam workshop (cosponsored by TSMC and Leti) at the event reviewed technical and business aspects of maskless lithography (ML2) technologies both in relation to direct wafer imaging and as a solution for high-speed mask writers. Approximately 70 litho technologists, mask fabricators, equipment suppliers, and development and manufacturing managers hashed out discussions on current status, plans, and timelines. Attendees also participated in a technical survey.

Among the key takeaway messages from the workshop, as provided by SEMATECH:

– Maskless litho has different potential applications in manufacturing: prototype development, low-volume production, critical layer mix & match, risk reduction, and pattern generator MBMW.

– For wafer writers, technical development continues in several areas:

- Mapper has shipped two pre-alpha tools;

- Demos of resolution down to 22nm;

- To date, no convergence on a single methodology

Top three issues that emerged from discussions:

- Throughput — beam current vs. throughput trade-off

- Beam calibration, verification, and inspection on wafer

- Beam stability/reliability

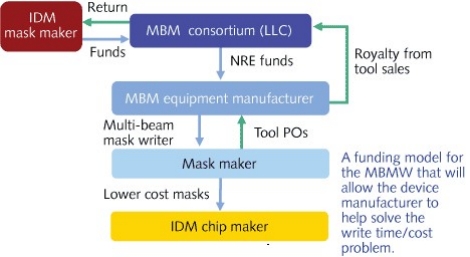

There is a strong market need for a multibeam mask writer, though there are multiple approaches to get there, including multicolumn and multibeam. As "a path forward" to meet maskwriters’ needs in the 2013-2014 timeframe, SEMATECH is proposing a consortium-based funding model for multibeam maskwriting, similar to its recently announced EUVL mask infrastructure (EMI) consortium (see chart below).