January 17, 2011 — Mark Durcan, president & COO of Micron, gave the conference keynote address at SEMI’s Industry Strategy Symposium (1/9-1/12/11, Half Moon Bay, CA). Afterward, he shared his thoughts on M&A strategy, Micron’s positioning for the future, and enthusiasm for the memory business with Debra Vogler, senior technical editor.

Listen to Durcan’s interview: Download (for iPhone/iPod users) or Play Now

Durcan spoke about leveraging capital efficiency for global leadership and reviews what he calls the “degrees of freedom” associated with leveraging capital appropriately: cost of technology, amount of capacity, timing, location, and cost of capital.

|

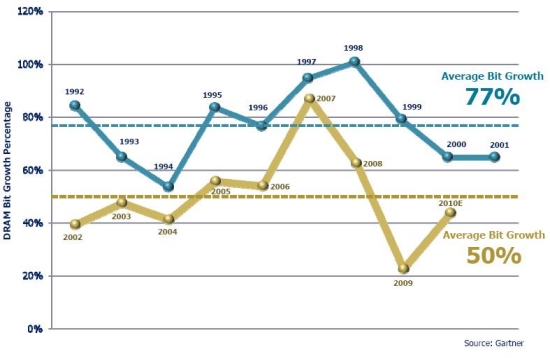

| Figure 1. DRAM bit growth. SOURCE: Gartner |

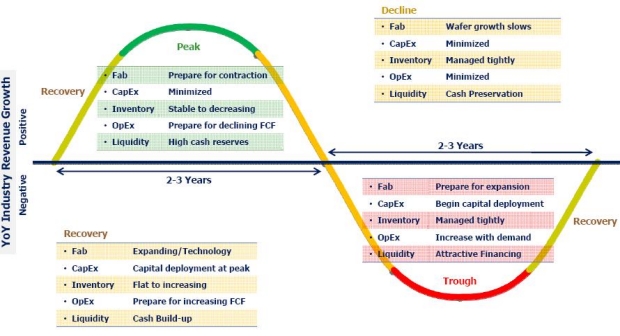

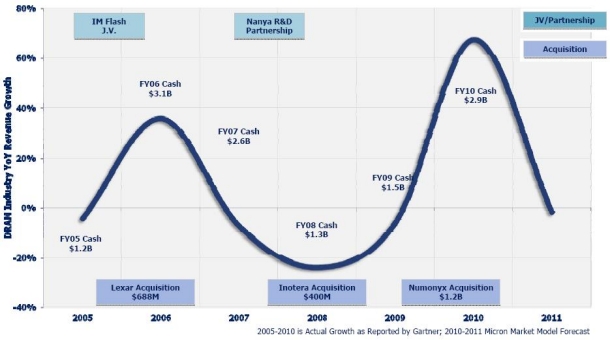

Regarding the DRAM space, Durcan explains Micron’s business strategy and how the company has managed itself within a reasonable average bit growth per year range (Fig. 1). He explains that investing in technology migration vs. capacity expansion provides a better match relative to supply and demand. Managing memory cycles is also critical to success (Fig. 2) and Durcan describes how Micron has positioned itself for the long haul. Part of Micron’s success is related to its M&A and partnership activity, as well as a countercyclical investment strategy (Fig. 3). Durcan discusses each of these in detail and how timing (in good times and in down cycles) is key to making the correct decisions.

|

| Figure 2. Managing memory cycles proactively is critical to success. SOURCE: Micron |

Despite all the challenges facing not only the memory segment — including the “memory wall” — but the semiconductor industry in total, Durcan is confident in the future. The company’s deployment of SSDs is a positive sign. Adoption of DDR3 has been slower than expected, however, and the company is actively addressing the challenges associated with this performance enhancer (i.e., limitations in the overall system architecture that impact latency) including adding memory tiers (between NVM and DRAM) and getting the memory closer to the processor (e.g., through silicon vias [TSV], new integration at the architectural level).

|

| Figure 3. Counter-cyclical investment strategy. SOURCE: Micron |

In other developments, the company’s end users are in the product definition phase of TSVs and the company is actively sampling TSV processes. The company is seeing strong acceptance and Durcan anticipates a manufacturing timeframe in about 18 months and beyond.

Subscribe to Solid State Technology/Advanced Packaging.

Follow Solid State Technology on Twitter.com via editors Pete Singer, twitter.com/PetesTweetsPW and Debra Vogler, twitter.com/dvogler_PV_semi.