By Debra Vogler, senior technical editor

March 16, 2011 — Synopsys introduced the Proteus LRC for lithography verification at the SPIE Advanced Lithography Conference (February 27 to March 3 in San Jose, CA). The new system provides comprehensive, process-window-aware checking features to identify locations in a design that are sensitive to process variations, thereby enabling corrective action to be taken prior to committing a design to manufacture.

|

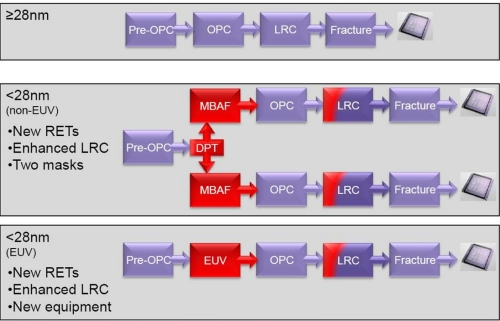

| Figure 1. The evolution of manufacturing flows. SOURCE: imec |

The product is integrated into the Proteus Mask Synthesis flow and suits use by OPC and mask data preparation groups. It is targeted for 28nm and below and includes EUV as well as double-patterning (DPT) capabilities. George Bailey, director, technical marketing at Synopsys, describes the data flow process (Fig. 1) in a podcast interview at the conference.

Listen to Bailey’s interview: Download (iPod/iPhone users) or Play Now

The large data volumes associated with EUV (e.g., flare corrections; full reticle layout) require a different data flow. “If you try to attempt that [data flow] in a traditional flow, you will have I/O issues…but with the pipeline, we do an upfront I/O, we decompose the layout, and we keep it decomposed through the whole process, all the way to mask data prep,” said Bailey. “So once the data base is broken down into templates, it remains in template form throughout the manufacturing flow.” This process eliminates intermediate I/O steps, noted Bailey.

|

|

|

| a) First-principle simulator for EUV and DPT: Predictive 3D resist profile modeling (SPIE 2010, 7641-9) | b) Proteus Pipeline integration enables full-reticle verification through concurrency and elimination of intermediate I/O | c) DPT-specific check functions for unique errors found in multi-mask processes |

| Figure 2. Proteus LRC ready for EUV and DPT. SOURCE: Synopsys and imec | ||

The product also includes the capability to handle the new failure modes associated with double-patterning (DPT) (i.e., overlay issues, modeling accuracy) (Fig. 2).

Also read: Synopsys lithography verification in Proteus LRC handles EUV, double patterning

Subscribe to Solid State Technology/Advanced Packaging.

Follow Solid State Technology on Twitter.com via editors Pete Singer, twitter.com/PetesTweetsPW and Debra Vogler, twitter.com/dvogler_PV_semi.