By Debra Vogler, senior technical editor

April 5, 2011 — Sharon Holt, SVP/GM, Semiconductor Business Group, Rambus Inc., opened up the GSA Memory Conference (3/31/11, San Jose, CA) by making the case for a kind of evolutionary revolution in memory — one that essentially unifies the memory requirements of PCs/servers as well as smart phones/tablets. In a podcast interview, Holt briefly summarized the kinds of innovations Rambus has made with respect to signaling, power management, and clocking and threading — all of which can be done without changing the semiconductor industry’s infrastructure.

Listen to Holt’s interview: Download or Play Now

Listen to Holt’s interview: Download or Play Now

|

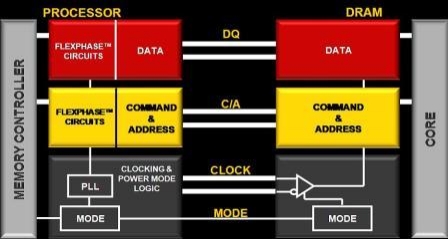

| Figure 1. Innovations: performance and power efficiency. Very low-swing differential signaling improves signal integrity, reduces active power, and enables higher data rates. FlexClocking architecture and advanced power state management reduces DRAM cost and complexity, power state transition times, and standby and overall power. |

Holt says that continuing to increase the speeds of LPDDR while staying in the tight power envelope required by both sets of memory requirements (PCs/servers and tablets/smart phones) can be a way to buy the industry more time before moving to the more revolutionary wide I/O memory with through silicon via (TSV) solution. Wide I/O interconnects would involve new infrastructure and financial considerations (liability issues — who owns what, when yield goes south) said Holt.

|

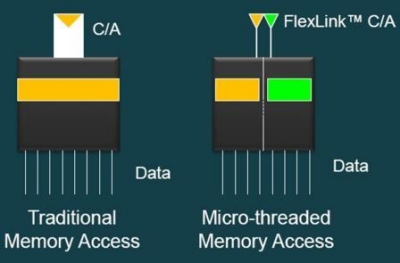

The FlexLink command/access (C/A) improves memory parallelism for multi-core processing, enables higher data rates, and improves memory system scalability.

The micro-threaded memory core improves data throughput, reduces memory resource contention, and enables finer access granularity. |

| Figure 2. Innovations: throughput. | |

By taking the evolutionary path, the industry will be able to work out the technical, infrastructure, and standards issues that go hand-in-hand with disruptive technologies.

|

|

|

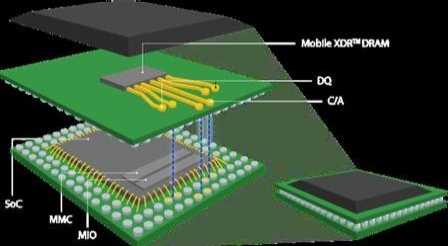

Figure 3. Architectural solution for mobile memory. Mobile XDR memory is tailored for compact package on package (PoP) implementations. |

|