|

Executive Overview

TSVs have the potential to open up many opportunities for economical, high-performance 3D packaging, but existing dry deposition methods present significant technical and economic limitations. In addition to high cost-of-ownership for proprietary cluster-tool platforms, dry deposition processes are unable to fill high-aspect-ratio vias, which creates a significant impediment to shrinking feature sizes in future technology generations. This paper outlines a wet-deposition approach to TSV fabrication, including results of reliability and purity testing, and the approach’s potential for process simplification.

|

Claudio Truzzi, Alchimer S.A., Massy, France

After many years as a hypothetical possibility, 3D IC stacking has emerged as a potential key enabler for maintaining semiconductor performance trends. Implementing 3D, however, will almost certainly require development of through-silicon vias (TSVs), which in the past few years have been elevated by the semiconductor industry to the status of a crucial mainstream technology.

Producing these vertical connections can seem misleadingly straightforward: drill a blind hole through the silicon wafer, deposit a uniform liner layer of dielectric material to electrically isolate the via, deposit a barrier layer to prevent copper from diffusing into silicon, and then completely fill the via with electro-chemically deposited (ECD) copper. An additional copper-seed layer may be needed before via filling if the selected barrier material is too resistive to allow the inception of the ECD process; as we will see, this is the case for most dry-process barriers, but not for all barrier materials [1]. CMP and wafer-thinning steps conclude the sequence.

While the process flow is relatively simple, the industry’s conventional approach to bringing it into volume production is, in essence, a patchwork attempt at implementing a revolutionary technology with an evolutionary attitude, using what’s available today from other fields and pushing the envelope to make it work for TSVs. This strategy is encumbering the industry with unnecessary limitations in terms of technology performance, manufacturing infrastructure, and cost, as well as a longer-term issue that is potentially even more problematic: scalability.

The default scenario for TSV fabrication leverages expensive vacuum-based, dry-process equipment and consumables, such as PE-CVD, iPVD, and ALD, which were originally designed for dual-damascene applications. This has put a tight limitation on TSVs’ maximum aspect ratio (AR, equal to via depth/diameter), and has created an artificial lockup of wafer thickness and via diameter. Common ARs today are limited to the 5:1 to 10:1 range – we’ll see later the reasons why. A minimum wafer thickness of 100µm will limit the minimum via diameter to more than 10µm for a 10:1 TSV. We could drill a 20µm TSV, but if we want a 5µm TSV, we’ll be forced to thin the wafers down to 50µm. That may be fine for process and equipment engineers, but if we turn our head and start talking to 3D-system designers, we’ll realize there are a number of reasons why bulky vias are not welcomed by that community:

- Stress (σ) in silicon bulk is linked to the square of the TSV radius R: if R is twice as large, σ increases fourfold [2].

- Also, larger σ leads to larger mobility shift in Si, degrading device performance.

- Parasitic capacitance and crosstalk are linearly dependent on R: if R doubles, their values double.

- On-chip real estate cost for TSVs is linked to R2: it will increase fourfold when R doubles.

But most importantly, designers want to make sure they don’t have to completely redesign their ICs at every new node just because the TSV diameter cannot be scaled down accordingly. They need scalable TSVs, i.e., a technology allowing via size to shrink with each new generation without affecting the wafer thickness in the process − or paying a 40% premium every time the TSV shrinks [3].

With the dry-process approach, cost increases with aspect ratio (or, assuming the depth doesn’t change, with decreasing via diameter): PVD is limited to AR <3:1; PE-PVD can address AR<6:1, and iPVD can be used for AR<8:1. How do we tackle ARs at 20:1 and above? The only apparent alternative is expensive and low-throughput ALD.

This brings us face-to-face with the fundamental limitation of the dry-process approach for TSVs: it is not future-proven. The maximum AR possible with dry-processed TSVs (10:1) is merely the minimum starting point required by designers today. The limitation comes essentially from the fact that most dry processing tools are based on a line-of-sight deposition methodology, which is intrinsically inappropriate for uniform top-to-bottom coating of narrow and deep holes. Many improvements or alternate methods have been proposed − they can often get the job done, but only at a premium, as we have seen.

TSVs are a revolutionary building block, with game-changing potential for the entire electronics value chain. Realizing their potential requires an equally disruptive approach to fabrication. That option exists today, in the form of a wet-process nanotechnology solution that offers precise control of formation and growth of the layers directly at the wafer surface, and uses standard plating tools in lieu of expensive vacuum-based equipment, cutting the costs by two thirds [4]. The wet-process approach allows the use of a single tool to line and fill TSVs with AR>20:1 at the same cost as AR<10:1.

This solution is based on two fundamental molecular engineering technologies: electrografting (eG) and chemicalgrafting (cG). The term "grafting" indicates the formation of strong chemical bonds at the molecular level between the underlying layer’s extreme surface (e.g., silicon) and the film being grown from that surface out (e.g., the isolation liner) [5].

Electrografting for TSVs

Electrografting [6] is a nanotechnology based on surface chemistry formulations and processes. It is compatible with conductive, semi-conductive and resistive surfaces, and enables self-oriented growth of thin coatings of various materials, initiated by in situ chemical reactions between specific precursor molecules and the surface.

For TSV applications, a polymer layer is directly grafted onto the silicon surface, yielding a highly conformal and adherent coating. This first grafted layer acts as an insulating layer as well as an adhesion promoter for the subsequent barrier layer deposition, which is performed by chemical grafting.

Chemical grafting is based on the same fundamental mechanisms as electrografting, and is used on non-conductive surfaces. Specific chemical groups have been chosen to strongly bond the barrier activator with the polymer. This improves adhesion between the barrier and the polymer through a chemical grafting step by creating a chain of chemical bonds from the substrate to the barrier. The barrier film is a NiB alloy, chosen because Ni-based barrier films present much lower resistivity values than conventional dry barriers. NiB chemical grafting barrier formulations have been optimized to reduce the resistivity value below 20µΩ/cm; this value makes it possible to eliminate the Cu seed layer, and, as described later, sets the stage for direct fill of the TSV from the barrier layer, further simplifying the TSV process sequence.

Electrografting deposition of a Cu seed layer, using a bath containing specific organics and copper, is also available, and has already been described [7,8]. It has been shown how an electrochemical process is applied to provide a conformal and continuous copper seed layer directly on various dry and wet barriers. It has already been proven that electrografting Cu seed layers meet or exceed all TSV requirements. For the remainder of this paper, we will focus on electrografting isolation and chemical grafting barrier.

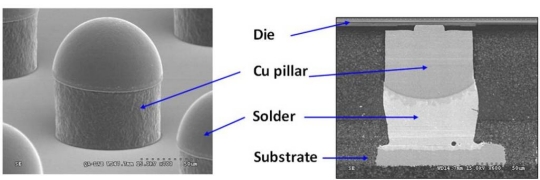

A single-step wet deposition method has been developed for nickel-based barriers on eG isolation and dry dielectric layers (such as SiO2, SiC, SiOC or SiN). This approach enables a cost-effective, streamlined process for via-middle and via-last applications, where TSVs are drilled through a stack of different materials. An example of one-step barrier deposition over eG isolation/SiO2 is shown in Fig. 1a.

|

|

Figure 1. SEM cross-sections of electrografting isolation and chemical grafting barrier: a) on top of a Si/SiO2 stack, and b) on top of the scalloped silicon surface.

|

Electrografting and chemical grafting formulations and processes fulfill all standard wafer fab requirements and safety guidelines and have been developed and specifically tailored to TSV diameters ranging from 1 to 200µm, covering a depth/diameter aspect ratio range from 1:1 to 20:1. Higher ARs are possible – an important consideration in the long-term scalability of the process. Layers made with electrografting and chemical grafting, activated from the surface, are not sensitive to topography, and fit perfectly well with the highly scalloped TSV sidewalls induced by the Bosch etching process (Fig. 1b).

Film properties

Film thickness can be controlled to any value from 40 to 400nm with maximum non-uniformity of 5% 3σ in-wafer (300mm). This provides a step coverage value (bottom/top thickness ratio) of up to 90% for liner and metal layers. As a reference, typical dry-process barrier step coverage values are below 10% for 10:1 aspect ratio TSVs. Adhesion of all layers was measured using a 16-squares scribe tape test method: all layers successfully passed the test. Film properties for each layer, as well as reliability test results, are discussed in detail in [1]. Selected basic film properties are summarized in Table 1. Barrier properties have already been described in [9] and proved to be equivalent to industry reference barriers.

|

| Table 1. Selected electrografting isolotion and chemical grafting barrier film properties compared with the industry baseline. |

New generation TSV copper fill

Filling narrow, deep vias without voids is not an easy task. Most commercially available chemistries encounter problems due to the sheet resistance (Rs) of the underlying layer. As noted earlier, this is the reason Cu-seed layers are required. However, because of the extremely poor step coverage of dry-process barrier and seed layers (<10%), sheet resistance values at the bottom of the via are very high, making it difficult to initiate the filling process. As a reference, current strongly acidic chemistries require Rs values smaller than 0.2Ω/sq, which converts to a minimum of 100nm thickness for the Cu seed layer.

Today, a new mildly basic TSV plating chemistry is available [10] based on the same nanotechnology concept described above. This TSV-grade chemistry is not sensitive to the sheet resistance of the underlying layer, and can be applied over Rs values as high as 50Ω/sq. It has very few contaminants and shows high uniformity on resistive layers. It is fully compatible with industry strandard wet-process tools and, in contrast with ECD solutions, it does not attack or degrade the underlying layer. Electrical and thickness uniformity of copper deposition at wafer scale in the first instants of the growth have been shown to have less than 10% non-uniformity after a few minutes of process.

|

|

Figure 2. Conformal isolation and barrier coating and void-free Cu filling of a narrow, 10:1 TSV using electrografting-based chemistries.

|

Copper grain size in deposited films has been analyzed by EBSD, XRD and self-anneal rate, showing similar values to conventional ECD chemistries. Stress was measured below 100MPa using conventional methods, which is lower than the industry baseline for ECD. Copper resistivity is 1.8µΩ.cm after anneal. Figure 2 shows a 10:1 TSV lined with wet-process isolation and barrier layers and filled with the new-generation TSV-grade Cu fill.

|

|

Figure 3. TOF-SIMS analysis of carbon (left) and chlorine (right) contaminant levels in bulk copper deposited with the new TSV-grade Cu vs. conventional ECD chemistry.

|

Contaminant levels have been measured by TOF-SIMS, focusing on C, S and Cl, and show much smaller values than typical acidic ECD chemistries, especially for chlorine (which is not part of the mildly basic chemistry formulation). Figure 3 shows an order-of-magnitude reduction in carbon contamination and a two orders-of-magnitude reduction in chlorine contamination for the new TSV-grade copper fill compared to conventional TSV chemistries.

Reliability tests

Specific test vehicles, with typical TSV design rules, were used to assess the reliability of an integrated stack of electrografting and chemical grafting layers filled with the mildly basic plating chemistry. Tests included temperature cycling (1,000 cycles from -55°C to 125°C), moisture sensitivity levels, high-temperature storage, thermal shock, and solder heat resistance. All samples passed the reliability tests. Figure 4 shows a SEM cross-section and a top view of filled structures after 1,000 thermal cycles. Additionally, electrografting layers have been integrated into test vehicles and exposed to autoclave (AC) and high-temperature storage (HTS) reliability testing. The autoclave test was conducted for 96 hours at 121°C, 100% relative humidity and 2 bar absolute pressure. High-temperature storage was performed for 20 hours at 205°C. Both tests showed positive results with no significant difference in film performance before and after the tests [11]

|

|

Figure 4. TSV structures lined with electrografting isolation and chemical grafting barrier, and filled with electrografting Cu, after 1,000 thermal cycles.

|

Conclusion

Electrografting nanotechnology has been optimized for highly conformal growth of TSV films. The technology is fully compatible with standard semiconductor plating tools, enabling a large reduction in cost-of-ownership per wafer compared to the dry process approach [4], while also providing stable and well-monitored chemical baths. Film properties meet or exceed current TSV requirements, and chemical formulations are production-ready. TSVs manufactured using electrografting can be very narrow and have aspect ratios up to 20:1, thus broadening the 3D-IC design space and offering a process solution that can be extended for at least several generations into the future.

Acknowledgments

eG and eC are trademarks of Alchimer S.A.

References

1. C. Truzzi, et al., "Wet-Process Deposition of TSV Liner and Metal Films," Proc. IEEE 3D System Integration, San Francisco, CA, Sep. 2009.

2 K.H. Lu, et al., "Thermal Stress Induced Delamination of Through Silicon Vias in 3D Interconnects," Proc. 60th ECTC, Las Vegas, NV, May 2010.

3. D. Velenis, et al., "Cost Effectiveness of 3D Integration Options," Proc. IEEE 3D System Integration Conf., Nov 16-18, 2010 Munich (D).

4. C. Truzzi, et al., "Electrografting – Unlocking High Aspect Ratio TSVs," Future Fab Intl., Issue 31, Oct. 2009.

5. S. Palacin, "Molecule-to-Metal Bonds: Electrografting Polymers on Conducting Surfaces," ChemPhysChem 2004, 5, 1468 – 1481.

6. D. Suhr, et al., "TSV metallization: a novel approach for insulation/barrier/copper seed layer deposition based on wet electrografting and chemical grafting technologies," Proc. MRS Fall Conf., Boston, MA, Dec. 2008, pp. 247-255.

7. S. Ledain, et al., "An evaluation of electrografted copper seed layers for enhanced metallization of deep TSV structures," Proc. 11th IEEE IITC, Burlingame, CA, June 2008, pp. 151-161.

8. F. Raynal, et al., "Electrografted seed layers for metallization of deep TSV structures," Proc. 59th ECTC, San Diego, CA, May 2009, pp. 1147-1152.

9. F. Raynal, et al., "‘Integration of Electrografted Layers for the Metallization of Deep TSVs." Jour. of Microelectronics and Electronic Packaging, Vol. 7, Number 3, 2010.

10. C. Truzzi, et al., "New Generation of Cost-effective Seedless Technologies for Through Silicon Vias," Proc. 20th Asian session Adv. Met. Conf., Oct. 20-22, 2010 Tokyo.

11. J. Reed, "Reliability Testing of High Aspect Ratio Through Silicon Vias Fabricated with Atomic Layer Deposition Barrier, Seed Layer and Direct Plating Deposition and Material Properties Characterization of Electrografted Insulator, Barrier and Seed Layers for 3-D Integration," Proc. IEEE 3D System Integration Conf. 2010, Nov 16-18, 2010 Munich (D).

Biography

Claudio Truzzi received his MS degree in electronic engineering from the U. of Bologna and a PhD in electronic engineering from the U. of Torino, and is the CTO of Alchimer S.A., Z.I. de la Bonde 15, rue du Buisson aux Fraises, 91300 Massy, France; ph.: +33 (0)1 69 75 43 43; email [email protected].

More Solid State Technology Current Issue Articles

More Solid State Technology Archives Issue Articles