by Dr. Phil Garrou, contributing editor

January 7, 2010 – On December 6th, Ziptronix Inc. filed a complaint of patent infringement against Omnivision Technologies, TSMC Ltd and TSMC North America in US District court, alleging that the defendants "willfully and deliberately infringed" on several patents pertaining to low-temperature oxide bonding.

Omnivision acknowledged the patent infringement complaint in its recent 10Q filing with the Securities and Exchange commission, and responded that they plan to "vigorously defend ourselves" against the allegations.

When asked for comment, Ziptronix CEO Dan Donabedian referred to the company’s "extensive patent portfolio" that enables manufacturing of backside illumination CMOS image sensors. "Ziptronix respects the intellectual property of others and expects others to do the same," he said, and pledged that the company "will vigorously monitor all acts of infringement and take the necessary actions to protect its intellectual property and the interests of its duly authorized licensees."

Founded in October 2000, Ziptronix was spun out from North Carolina’s RTI International for the purpose of commercializing wafer and die bonding technology. In the intervening years, such technologies have found an important role in the evolving areas of chip-on-chip (CoC) bonding, 3D IC integration, and CMOS image sensing.

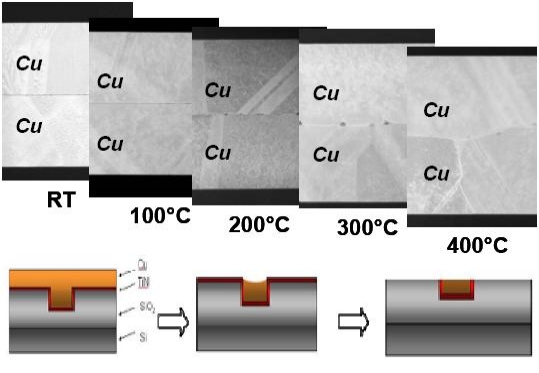

Ziptronix’s patent portfolio is centered around its ZiBond (Ziptronix bonding) and DBI (direct bond interconnect) technologies. ZiBond is based on their discovery that one can achieve significantly higher bond energy between wafers (with thermal or other oxide) after treatment with various surface "activating and terminating" processes. The direct oxide bonding, which is initiated at low temperature, is characterized by a very high bond energy between the surfaces.

In 2008, Donabedian offered a warning that "the broad and fundamental nature of our patent portfolio leads us to believe that any use of a oxide low-temperature bonding process is highly likely to be covered by one or more of our patents."[1]. While acknowledging the availability of some commercial tools that claim to support low-temperature oxide bonding processes, the company had neither granted nor intended to grant any IP licenses to equipment manufacturers. "Anyone running a low-temperature oxide bonding process as part of their manufacturing scheme is likely to be infringing on our IP," he said.[2] In Nov. 2009 Raytheon Vision Systems reached a licensing agreement for the use of Ziptronix’ DBI technology in Raytheon’s imaging systems.

[1] "3D Startup Proves Ahead of Its Time", Semiconductor International, Oct. 2008

[2] "Ziptronix Pioneering 3D Integrated Circuit Process Technology", i-Micronews, Aug. 2008