May 13, 2011 — The ConFab gathers semiconductor industry leaders to discuss the biggest trends in the chip manufacturing sector. One of these major trends is 3D packaging. In Session 2 on Monday (May 16), John Waite (GLOBALFOUNDRIES), Raj Pendse (STATS ChipPAC), Robert Darveaux (Amkor), and Nick Yu (Qualcomm) will combine fabless, foundry, and packaging house perspectives on the disruptive design and process changes that 3D creates for the semiconductor and packaging industries.

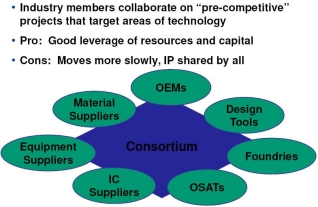

John Chen (Nvidia), Jeong-ki Min (Samsung Electronics), and Abraham Yee (Nvidia) will lead "Collaboration to Strengthen the IC Supply Chain."

Smaller dimensions and higher complexity chips are driving "More Moore," while "More than Moore" is pushing vertical integration, such as 3D TSV. Both require changes to the traditional frontend and backend of semiconductor manufacturing.

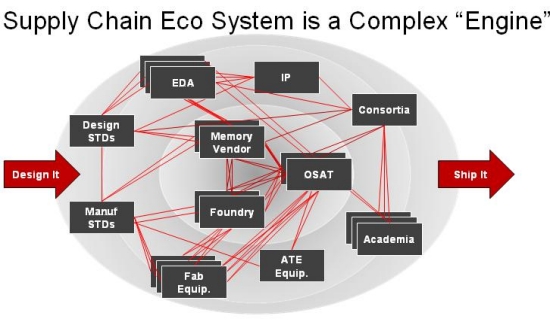

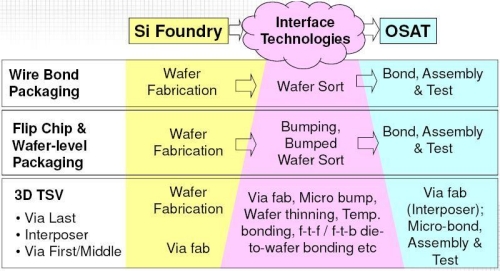

3D packaging, whether bonded wafers with through silicon vias (TSV) or wire bonded chip stacks, push packaging processes into the fab, and make wafer-level processes the outsourced semiconductor assembly and test (OSAT) provider’s responsibility. In this new supply chain, many questions are raised about ownership and responsibility in the implementation of a new chip design. Since our IC industry has long been divided into EDA or fab tool supplier, fabless, foundry and assembly/test companies, getting everyone to work together and make profits for each party can be extremely challenging. This session is intended to explore various options.

Session 2, "Collaboration to Strengthen the IC Supply Chain" presentations:

John Waite, VP, packaging development & central engineering, GLOBALFOUNDRIES: Waite will present "Supply Chain Reaction: A Collaborative Approach to Packaging Innovation." As the industry moves aggressively to more advanced technology nodes, the once "bland" interconnect, assembly and packaging processes can now improve performance and power efficiency as well as reduce costs for chip designers. Chip-package interaction (CPI) is significantly more complex today, requiring coordination between design and manufacturing. It is increasingly difficult for foundries and OSATs to be able to deliver end-to-end solutions that meet the requirements of leading-edge designs. A new approach is needed — one that leverages the success of a "shared investment, shared return" model.

Raj Pendse, VP product & technology marketing, STATS ChipPAC: Pendse will present "3D Packaging Evolution from an OSAT Perspective," illustrating the synergies and intersections among packaging technologies (i.e. traditional die and package stacking on substrates, fan-in and fan-out wafer level packaging and 3D Si integration) and the resulting future path for packaging technology. Pendse will discuss the transformed role of the OSAT industry in supporting this evolution. Latest developments in wafer thinning, micro bumping, micro bonding and logical hand off points among Si and package foundries will be presented, and Pendse will look at "bridge" technologies — interposers, TSV substrates — that play an interim role in the commercialization of 3D.

Robert Darveaux, CTO, Amkor: Darveaux will present "Supply Chain Challenges for 3D Integration of Memory and Logic Devices using TSVs." While package-on-package (POP) technology allows ease of test, flexible sourcing, and mature interconnect technology, TSV technology suffers from difficult-to-test high-density area array contact pads or bumps; bare or partially assembled memory and logic die that are difficult to burn in adequately; a newer joining technology not widely available to OEMs and contract assemblers; a poorly characterized joining process yield; and ultimately unclear ownership of defect liability. These problems can not be resolved by technologies or business models alone.

Nick Yu, VP of technology development, Qualcomm: Yu is presenting "3D Through Si Stacking Technology – a Qualcomm Perspective." Qualcomm, as an integrated fabless company, has several primary motivations for following 3D TSV-based stacking technologies. Yu will propose a roadmap for the evolution of the 3D technology, and detail the integration challenges for an integrated fabless manufacturer using a distributed supply chain. Yu shares Qualcomm’s implementation strategy, and points to some of the gaps in the business model associated with 3D products.

See The ConFab’s conference program here.

Bios:

Session Leaders:

John Chen, Ph.D., VP of technology and foundry operations, Nvidia: Dr. Chen has 30 years of experience in IC industry ranging from IDM to Foundry to Fabless companies. Dr. Chen was a Howard Hughes Doctor Fellow and received a Ph.D. in EE and an Executive Management degree, both from UCLA. He also holds a M.S. from University of Maine and a B.S. from National Taiwan University, both in E.E. He started his career as a researcher in Hughes Research Laboratories, subsequently at Xerox Palo Alto Research Center (PARC). Most of his work involves CMOS devices and process technologies. Later, he has had various technical and managerial positions in technology development and IC manufacturing. He has held positions at Cypress Semiconductor, TSMC, WaferTech (a JV then led by TSMC), and Nvidia. Dr. Chen has published 100 papers, mostly by IEEE and a book, "CMOS Devices and Technology for VLSI." Accolades and industry service include IEEE Fellow, Technical Advisory Committee for ITRI, Taiwan, and committee member of SIA and GSA.

Jeong-ki Min, VP of foundry marketing, Samsung Electronics Co., Ltd. LSI Division: Jeong-ki Min joined Samsung in 1984 and has served in marketing, technology planning, and capital investment to M&A and other strategic alliances. He also worked for Samsung’s US operations (San Jose, CA), as a planning officer. Min leads foundry and ASIC marketing teams and his current responsibility at System LSI Division includes business development and market research and customer engineering supports.

Abraham Yee, director of advanced technology & package development, Nvidia Corporation: Yee is responsible for readying next generation technologies for production, benchmarking technologies, investigating new technologies and setting NVIDIA’s process roadmap. Prior to NVIDIA, he has worked with SUN Microsystems, Equator Technologies, and LSI Logic Corp. Dr. Yee received his BA in Mathematics and Physics and his PhD in Physics from UC Berkeley.

Speakers:

Waite is responsible for global packaging development and collaborative R&D activities, as well as central engineering. Waite joined GLOBALFOUNDRIES in 2009 after a 25-year career in technical and management positions at AMD and IBM.

Pendse completed his BS in Materials Science from IIT Bombay with Top in Class honors and his Doctorate in Materials Science from UC Berkeley. Prior to joining STATS ChipPAC, Raj held various positions in package engineering and R&D at National Semiconductor Corp and Hewlett-Packard Labs. His work has spanned the gamut from packaging of high-end microprocessors, ASIC and graphics products to low-cost packaging solutions for logic and analog devices used in mobile phones and consumer products. His most recent focus has been on flip chip and 3D wafer level packaging.

Darveaux has 24 years experience in the IC packaging field at the Microelectronics Center of North Carolina, Motorola, and Amkor. Robert has a B.S. in Nuclear Engineering from Iowa State University and a Ph.D. in Materials Science and Engineering from North Carolina State University. His expertise covers thermal and mechanical simulation, materials characterization, failure analysis, and fatigue life prediction for solder joints. Robert has published over 75 technical papers and has 22 patents.

Yu is a Vice President of Engineering at Qualcomm’s CDMA Technologies Division. He sets Qualcomm’s semiconductor technology roadmaps including wafer fab process node, backend interconnect and packaging technologies. Yu has 18 years of experience with Qualcomm on low power wireless chipset and SoC development. He is one of the architects of, and has participated in the definition and development of, many Qualcomm chipset products. Nick has an MSEE degree from Georgia Institute of Technology.