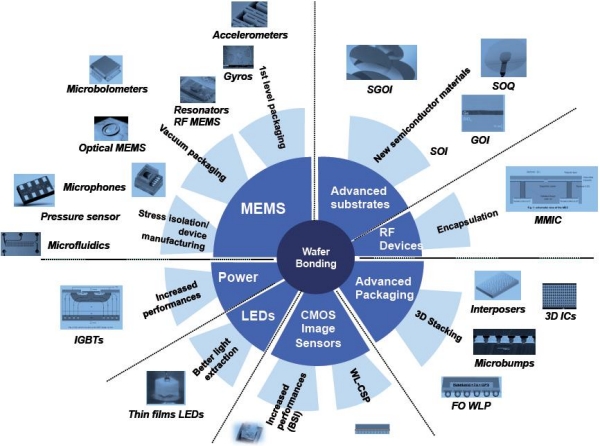

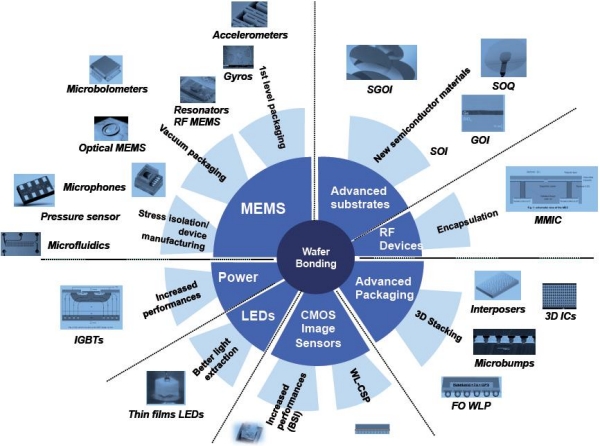

May 17, 2011 — Wafer bonding is a complex process, used on 2" to 12" wafers for MEMS, CMOS image sensors, advanced packaging, LEDs, and other chips. Yole Développement published a technology study and market research report, "Permanent wafer bonding," to derive trends in the market and technology through 2016. The report aims at analyzing the market perspectives and technical trends for permanent bonding.

Yole Développement has estimated that the wafer bonding market will grow significantly for the next year. The growth will be driven small-size wafers for LEDs and 12" wafers for 3D die stacking and CIS.

The wafer bonding market is a very complex one, crossing different wafer sizes (from 2" to 12"), different applications (MEMS, CMOS image sensors [CIS], LEDs, power devices, RF and advanced packaging), and different bonding technologies (adhesive, anodic, fusion, direct oxide, eutectic, glass frit, metal diffusion).

Wafer bonding is usually defined as a process that temporarily or permanently joins two wafers or substrates using a suitable process. Historically developed for MEMS and then SOI wafers, wafer bonding technology has shifted to non-mainstream IC applications over the last years.

"MEMS has been the first application where wafer bonders have been massively used (the wafer bonding step is mostly used to protect the MEMS sensitive element), explained Dr Eric Mounier, project manager at Yole Développement. MEMS manufacturers are currently shifting from glass frit for eutectic/metal-based bonding, yielding smaller bond frames. Metal direct bonding also provides hermeticity and mechanical stability for many MEMS applications. For example, Nasiri uses eutectic bonding of the MEMS directly on the aluminum layer of the CMOS wafer. This leads to smaller package footprints & package heights. STMicroelectronics’ latest 3-axis accelerometer (LIS3DH) also shows a new sealing technique: gold eutectic sealing allows a dramatic die size reduction.

CMOS image sensors are also a strong wafer bonding application. Up to two different wafer bonding steps can be necessary for next-generation CMOS image sensor fab: one for back-side illumination, the second for wafer-level chipscale packaging (WLCSP). For CIS, the advent of backside illumination (BSI) technology has raised a competition between molecular bonding and adhesive bonding. Here, cost and final application will drive the final technology choice.

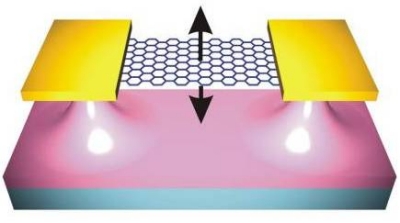

Besides MEMS and CIS manufacturing, wafer bonding also can be used for LED and power device fab. In a typical LED active region, spontaneous emission scatters photons in all directions. If the substrate material has a smaller band gap than the active region, approximately half of the light is absorbed in the substrate; significantly reducing device performance. So, one of the manufacturing solutions for photon loss involves bonding a wafer containing an array of devices to another wafer that provides both a reflective surface for maximum light extraction and a heatsink for thermal management.

|

Companies cited in the report:

Acreo, AML, APM/UMC, Avago, Ayumi, Bosch, Colibrys, Dalsa, Discera, EVGroup, FhG IMS, FLIR, IBM, Icemos, IMEC, IMT, Infineon, Infineon, Invensense, KTH, Leti, Lumileds, MEMStech, Micralyne, Mitsubishi Heavy Industries, Okmetic, Omron, Osram, Qualcomm, Raytheon, RPI, Sand9, Semefab, Sensonor, Silex, SOITEC, STM, SUSS MicroTEC, Tezzaron, TI, tMt, Tohoku University, TowerJazz, Tracit, Triquint, Tronic’s, TSMC, VTI, Xcom, Ziptronix

|

Over the 5 past years, much attention has been given to wafer bonding for 3D integration of memories, for example, and other die.

Although EV Group (EVG) is the market leader in permanent bonding, the growth of the bonding equipment market is attracting challengers.

Yole Développement’s report analyzes the technical & economical evolution of the permanent wafer bonding process. It gives 2010-2016 market forecasts for permanent bonding, equipment, an overview of the different bonding approaches and equipment players market shares and competitive information, This market & technology report also presents the trends for permanent bonding, wafer-to-wafer (W2W) vs. chip-to-wafer (C2W) analysis for 3D integration. It describes the applications for wafer bonding with main characteristics and challenges.

Report author:

Dr. Eric Mounier has a PhD in microelectronics from the INPG in Grenoble. Since 1998 he is a co-founder of Yole Développement, a market research company based in France. At Yole Développement, Dr. Eric Mounier is in charge of market analysis for MEMS, equipment & material. Yole Développement is a group of companies providing market research, technology analysis, strategy consulting, media in addition to finance services. Learn more at www.yole.fr

Subscribe to Solid State Technology/Advanced Packaging.

Follow Advanced Packaging on Twitter.com by clicking www.twitter.com/advpackaging. Or join our Facebook group