May 17, 2011 — The Binnig and Rohrer Nanotechnology Center opened at IBM (NYSE: IBM) Research – Zurich. with 600 guests from industry, academia, and governments. ETH Zurich, a European science and engineering university, and IBM have collaborated for 10 years on nanoscience. Now, the Center will allow scientists from IBM and the university to research novel nanoscale structures and devices to advance energy and information technologies. EMPA, a Swiss national research institution under the umbrella of the ETH domain, also is a partner in the new center.

The Center is named for Gerd Binnig and Heinrich Rohrer, two IBM scientists and Nobel Laureates (1986) who invented the scanning tunneling microscope at the Zurich Research Lab in 1981, thus enabling researchers to see atoms on a surface for the first time. Their work on microscopy tools has allowed researchers to visualize the nanoscale. The two scientists attended today’s opening ceremony, at which the new lab was unveiled to the public. Binnig told Small Times in 2003 that he still recalls what it felt like in 1981 when he tested his technical innovations and saw atomic structures for the first time. "It was like a dream to discover all this," said Binnig, a fellow at IBM Zurich Research Laboratory. "It was like being for the first time on the moon."

The Binnig and Rohrer Nanotechnology Center offers a cutting-edge, collaborative infrastructure designed specifically for advancing nanoscience. The noise-free labs open up a new level of precision, thereby potentially extending the scale on which scientists are able to measure and experiment even further.

A large cleanroom for micro and nanofabrication provides scientists from IBM and ETH Zurich with a flexible environment and tools for lithography, wet processing, dry etching, thermal processes, thin-film deposition or metrology and characterization. The cleanroom also features a special area for processing carbon-based materials and structures.

Six uniquely designed noise-free labs shield extremely sensitive experiments from external disturbances, such as vibrations, electro-magnetic fields, for example from nearby trains and cellphone towers, temperature fluctuations and acoustic noise.

The new Nanotechnology Center has been granted the use of the Minergie quality label, a Swiss standard for sustainable and energy-efficient buildings. Photovoltaics, geothermal probes, and heat recovery windows are part of this efficiency.

The building represents an investment of $60 million in infrastructure costs and an additional $30 million for tooling and equipment which, including the operating costs, are shared by the partners.*

Scientists and engineers from IBM and ETH Zurich will pursue joint and independent projects, ranging from exploratory research to applied and near-term projects including new nanoscale devices and device concepts as well as generating insights about their scientific foundations at the atomic level. Three ETH professors and their teams have moved into the new building and will conduct part of their research in nanoscience on a permanent base. Even more ETH researchers will benefit from the partnership and be able to use the excellent infrastructure for various projects.

One focus of IBM’s research in the Center is put on exploring the "next switch"– the future building blocks for better, faster and more energy efficient chips and computer systems. For example, IBM scientists are currently exploring semiconducting nanowires to potentially increase the energy efficiency of computing devices by 10 times. In addition, through novel device concepts, such nanowires-transistors could virtually consume zero energy while in passive or standby mode.

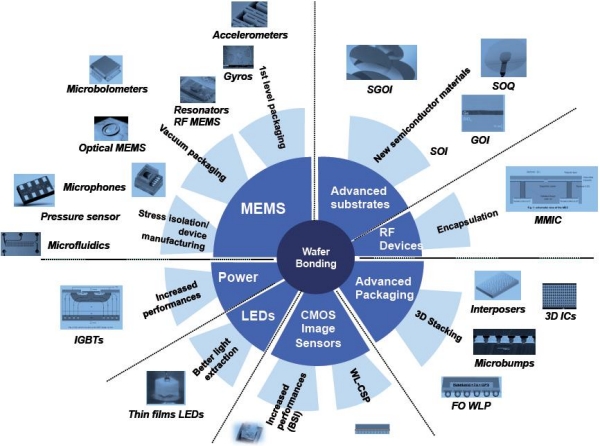

Additional research areas include micro- and nanoelectromechanical systems (MEMS/NEMS), spintronics, organic electronics, carbon-based devices, functional materials, cooling, three-dimensional integration of computer chips, opto-electronics and optical data communication in computers as well as silicon nanophotonics.

Researchers will also explore new approaches for fabricating structures and devices with dimensions down to a few nanometers, such as scanning-probe nanolithography or directed self-assembly, addressing the upcoming challenges for manufacturing at the nanoscale.

In addition to these partnerships, IBM will also collaborate in the Center with scientists from several Lithuanian universities, under a five-year agreement that was signed in September 2010 with the Lithuanian Ministry of Economy and Ministry of Education and Science. This collaboration will focus on integrated photonics and novel photonic materials to create faster computers, improved solar technologies, and nanopatterning security tags for advanced anti-forgery technology.

Throughout 2011, IBM will host the IBM Research Colloquia, convening thought leaders at its global labs to discuss technologies of the future and their potential impact on business and society. The first of these colloquia took place today at IBM Research – Zurich, and featured a dialogue on Nanotechnology and the Future of Computing with IBM Fellows and Nobel Laureates, Drs. Gerd Binnig and Heinrich Rohrer, and talks by Prof. Dr. Achim Bachem of the Julich Research Center on 21st Century Supercomputing; Prof. Dr. Karlheinz Meier, Kirchhoff Institute for Physics at Heidelberg University on Brain Inspired Computing and Prof. Dr. Daniel Loss of the University of Basel on Quantum Computing.

Learn more about the Center at http://www.zurich.ibm.com/nanocenter/factsheet.html

* the investment figure is based on an average conversion rate with Swiss Francs (CHF) between April 2008 – April 2011

Scientists can use the tool to evaluate crystallization and reorganization processes of materials, for example, how materials respond to rapid cooling in modern high-speed production processes. The FDSC operates at extremely high cooling (-4,000ºC/sec) and heating (40,000ºC/sec) rates. Very fast cooling and heating rates allow researchers to generate material under real process conditions (on cooling) and then measure those material properties (on heating).

Scientists can use the tool to evaluate crystallization and reorganization processes of materials, for example, how materials respond to rapid cooling in modern high-speed production processes. The FDSC operates at extremely high cooling (-4,000ºC/sec) and heating (40,000ºC/sec) rates. Very fast cooling and heating rates allow researchers to generate material under real process conditions (on cooling) and then measure those material properties (on heating).