Emerging technologies, such as imbedding components within organic substrates, fulfill challenging electronics design objectives. Imbedded component/die technology* is a method of imbedding active and passives into cavities within a multi-layer printed circuit board (PCB) to decrease the surface area required to implement the circuit design and increase the robustness of the overall assembly. Casey H. Cooper, STI Electronics Inc., discusses the design methodology, packaging processes, and test data gathered during imbedded die/component packaging implementation in a mixed-signal prototype. The prototype was subjected to reliability testing and ultimately demonstrated in a test flight. Test results are provided here.

The electronics industry has seen an explosion in development of new materials and processes to support “smaller, lighter, faster, and better” products. Military and aerospace electronics providers continue to push the technological envelope, designing and manufacturing leading-edge high-reliability electronics. Current design problems are not caused by circuit design capabilities but by an inability to reliably package these circuits within the space constraints. Innovative packaging techniques are required to meet the increasing size, weight, power, and reliability requirements of this industry without sacrificing electrical, mechanical, or thermal performance.

Over the last decade, advanced packaging technologies have shifted to 3D integration.1 Whereas most new products have defined X and Y dimensions, added capability is left confined to integration within these boundaries, forcing engineers to rely on miniaturization that can only be achieved through smaller form and fit factor components and interconnection in the Z direction. Some established packaging technologies integrate bare die of both actives and passives into package designs, such as multichip modules (MCM), system-in-package (SiP), chip-on-board (COB), and emerging system-level designs such as imbedded components.2

In a paper presented at SMTA’s Pan Pacific Conference in 2004, the features and advantages of imbedding actives and passives were described.3 Since then, development was completed on an imbedded die manufacturing process,4 imbedding unpackaged components, i.e. bare die, for further electronics hardware miniaturization than current packaging technologies, such as SMT, cannot provide.

This embedded packaging approach addresses miniaturization, thermal management, performance, reliability, and system capability requirements through innovative design guidelines and materials selection. Elimination of external component packaging reduces circuit card assembly (CCA) size, weight, and electrical and thermal parasitics, and it enables the 3D assembly of multiple components. 3D assembly facilitates design integration of key subsystems, i.e. multiple CCAs, into a single high-density module.

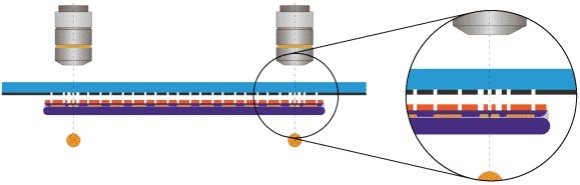

Miniaturization is achieved fundamentally due to the elimination of external component packaging. Bare die enable designers to specify the smallest form and fit factor available. Component geometries can be reduced up to 85% through the removal of external leadframes, package substrates, and overmold encapsulants. These die are then imbedded in openings/cut-outs of the PCB, commonly referred to as cavities (Figure 1). Imbedding die in cavities in the substrate facilitates Z-integration through imbedding die on tiers, or exposed layers, within the substrate.

|

| Figure 1. Active and passive components imbedded in a cavity on a laminate substrate. |

With the free real estate on the PCB provided by reduced component footprints, additional systems or capabilities can be added to an electronics assembly. System capabilities can be increased through the integration of additional features and functionality and/or redundant system within the same envelope. For example, processing architectures, such as those implemented in field programmable gate arrays (FPGAs), may be easily scaled to increase the number of processing elements within the same PCB envelope due to component-level miniaturization.

Elimination of secondary packaging materials plays a significant role in overall weight reduction achieved through imbedding unpackaged die. Interconnect materials that physically and electrically connect the bare die integrated circuit (IC) to the circuit are eliminated. There is also a reduction in the mass related to the electrical interconnect material, achieved by using wire bonds rather than solder. Typical bonding wire alloys have a lower density than solder, and wire bonds use a significantly lower volume of material per connection.

End-product reliability is improved not only by a reduction in attachment material mass through the elimination of external component packaging, but also through the increased flexibility of the electrical attachment. By using wire bonding technology as the electrical attachment process, very flexible light-weight interconnects are created. This flexibility is exploited during operation in demanding thermal and mechanical environments such as high temperature, vibration, and/or mechanical shock. In contrast to a soldered connection, which localizes the applied stress, the imbedded package concept distributes the applied stress producing a more robust and rugged electrical product.

Embedding actives and passives into the PCB improves long-term signal reliability by eliminating unnecessary failure opportunities and utilizing reliable electrical interconnects. All first-level component packaging is eliminated. This reduces two to four possible modes of electrical failure associated with component-level packaging. Due to the removal of external packaging, electrical parasitics and thermal resistance are reduced, improving overall system performance. This means the assembly is suitable for high-speed, high-I/O electronics, such as those found in missile defense systems.

Conventionally, a high-power CCA would dissipate heat through convection or radiation from the component and substrate surfaces, often including package-level heat sinks or cooling fans. However, advanced handheld applications inhibit the use of active cooling devices such as large, finned heatsinks and fans. Imbedded die/component technology relies on passive cooling via conduction to a single, central cooling core to remove heat from high-power devices and to evenly distribute the thermal energy along the interface. Through creative thermal management, die junction temperatures (TJ) are reduced, increasing package- and system-level reliability.3

Prototypes

We recently completed testing of two prototype vehicles to provide a technology demonstration of the design guidelines, materials, and manufacturing processes used to imbed passive and active devices in laminate substrates. Environmental stress testing was conducted on these prototypes to evaluate the robustness of imbedded bare die in an organic laminate substrate in conventional military and aerospace environments, i.e. harsh environments.

Test vehicle 1. A test vehicle was designed to evaluate the effectiveness of assembly materials in harsh environments when imbedding bare die (silicon) in organic laminate substrates. The test vehicle consisted of multiple imbedded die (Figure 2) wired to inner layer tiers for monitoring fluctuations in resistance during/after environmental testing. The imbedded test die consisted of silicon, daisy-chain components with peripheral bond pads for interconnecting to a test substrate. Test patterns on the high-temperature FR-4 (HT-FR4) laminate substrate enabled in-situ resistance monitoring of the assembly during testing. A conformal coating, encapsulant, and lid were used (Figure 3) to protect the imbedded die from physical damage (handling/transportation) and environments (thermal movement due to coefficient of thermal expansion (CTE) mismatch, ionic contamination, and moisture ingression).

The test coupon comprised a 4.000 × 6.000″ HT-FR4 substrate, laminate PCB, in three tiers, with an imbedded copper core and Ni/Au plating. The Si die was 0.248 × 0.240″, daisy-chain design, with peripheral wire bond pads. The die attach material was thermally conductive, electrically insulative compliant epoxy. A 1.2-mil-diameter Al/1%Si wire formed each interconnect. Conformal coating was achieved with a 0.6-mil-thick parylene C material; encapsulation used silicone gel to a 95% cavity fill. The lid was laminate with top/bottom copper plane layer.

|

| Figure 2. High-resolution images of test coupon daisy-chain die in the central cavity: upper left die (left) and lower left die (right). |

|

| Figure 3. High-resolution image of test coupon final assembly. |

Materials properties found on the technical data sheets were reviewed prior to selection of die attach, conformal coating, and encapsulant candidates to include in the test matrix. Materials were identified that minimize CTE-induced stress on the devices and interconnects and to reduce the thermal resistance between the die junctions and substrate/heat sink. Certain characteristics are desirable for all materials comprising the assembly. Materials with a glass transition temperature (Tg) outside the operating environment range can minimize thermomechanical stresses induced by a material’s state change from glassy to rubbery. Die attaches, underfills, and encapsulants with low ionic contaminates minimize opportunities for corrosion in harsh environments. Materials’ thermal and electrical performance equally contribute to system-level performance requirements. Materials meeting the following specifications were selected to be included in the test matrix.

Critical material properties:

- Cure temperature: The type of cure, snap cure versus a step cure, and cure temperature affect the cured material properties including Tg. The glass transition temperature should be significantly above the upper operating temperature range of the assembly to enable lower expansion/CTE of the material over a wider temperature range.5

- Material purity: Low ionic contaminants and alpha particles emitted will aid in increasing the reliability of the bare die. Industry recommends chloride (Cl-), sodium (Na+), potassium (K+), and fluorine (F-) levels of less than 5 to 10 ppm to increase the die’s resistance to corrosion.6 Less than 0.001 particles/cm2/hr minimizes irradiating particles found in encapsulants that can cause soft errors in logic and high-density memory devices such as DRAMs and SRAMS.7

- Voiding: Voids, or air pockets in the material, result in increased localized stresses, which can lead to premature delamination or loss of adhesion to the die and/or substrate. The material is no longer an effective stress buffer with voids present, and the material’s thermal resistance is increased due to air’s poor ability to transfer heat.

- Moisture absorption: Due to use of organic substrate materials, a hermetically sealed assembly cannot be achieved, thus the materials selected should be hydrophobic in nature.8

- One-part system: One-part materials are easily integrated into the manufacturing and assembly process. All components of the material, curing agent, and hardener, are premixed ensure product uniformity and quality and eliminate operator errors. The material is supplied in a syringe for use on automated dispensing equipment and is typically stored at -40ºC to prevent changes in performance.

Thermal cycling fatigue or overstress failures are often detected through alternating exposure of the assembly to extreme temperatures with short transition times between extremes. The test vehicle was placed in a thermal shock chamber to evaluate the materials’ resistance to temperature excursions and the process parameters used to assemble the test vehicle. The assembly was placed on a tray that transitions from a cold chamber (air) to a hot chamber (air) within a specified time. Test conditions were changed periodically during the thermal shock test. Test conditions included: 1000 cycles from -55°C to 85°C, 250 cycles from -55°C to 125°C, 200 cycles from -55°C to 85°C, followed by 4200 cycles from -55°C to 125°C. The test vehicle was subjected to over 175 days of thermal shock cycling.

Critical materials evaluated during this analysis included:

- Die attach adhesive: Determine effect of stress-related cracking of silicon die due to mismatch in coefficient of thermal expansion (CTE) of die and laminate/copper core.

- Conformal coating: Determine aging characteristics of Parylene after repeated exposure to extreme temperatures.

- Encapsulant: determine warpage and stress due to modulus and CTE differential of encapsulant and assembly (silicon die, laminate substrate, metal core, aluminum wire bonds).

Continuity testing was performed prior to cycling to establish a baseline resistance for each of the daisy-chains and at periodic intervals to monitor resistance fluctuations. Five daisy-chain die were imbedded within the test coupon, providing 30 daisy-chains, equivalent to 60 wires (120 wire bonds), for monitoring. A 3.0? increase in resistance constituted a failure with the cycles-to-failure data noted in Table 1. The first failure/high-resistance bond occurred after exposure to 3000 cycles with a lapse of 1500 cycles till the second noted failure. Only 23% of the wires failed after 5500 cycles when the test coupon was pulled from cycling.

Table 1. Thermal shock failure data for daisy-chain wires.

| Daisy-chain wire group |

Cycles |

Wire Group |

Cycles |

| 1 |

3,057 |

16 |

none |

| 2 |

4,507 |

17 |

none |

| 3 |

4,507 |

18 |

none |

| 4 |

4,947 |

19 |

none |

| 5 |

5,102 |

20 |

none |

| 6 |

5,656 |

21 |

none |

| 7 |

5,656 |

22 |

none |

| 8 |

none |

23 |

none |

| 9 |

none |

24 |

none |

| 10 |

none |

25 |

none |

| 11 |

none |

26 |

none |

| 12 |

none |

27 |

none |

| 13 |

none |

28 |

none |

| 14 |

none |

29 |

none |

| 15 |

none |

30 |

none |

The failure data gathered from this test vehicle indicates that the material properties selected will provide the long-term reliability solution for critical military electronics hardware. Compliant die attach adhesive enables stress relief from thermal-induced stress in the silicon-die-to-substrate interface while the wire bonds, coupled with a compliant encapsulant, provide the stress relief from environmental-induced stress (thermal, shock, and vibration). This material set, in conjunction with the imbedding design guidelines, enables robust, reliable electronics assemblies.

Test vehicle 2. A mixed-signal test vehicle (Figure 4) was designed and assembled to serve as a technology demonstration for the Navy’s Standard Missile-2 (SM-2) program. The Navy’s SM Program Office used this prototype in a flight test to support a technology demonstration of the imbedded component/die technology, validating the electrical and mechanical performance. A prototype was designed with a mix of analog and RF circuitry using imbedded design practices with wire-bondable devices. The prototype circuit design was selected to address miniaturization, thermal dissipation, component obsolescence, and reliability.

|

| Figure 4. Mixed-signal prototype to demonstrate IC/DT packaging technology’s capabilities. |

Miniaturization objectives were largely achieved due to the ability to locate wire-bondable components for the circuit. All ICs were procured as unpackaged components (wire bond/face-up die), and passives with gold metallization were procured for imbedding into the prototype. Through elimination of the secondary packaging, a 66% reduction in surface area was achieved. This reduction enables the integration of future CCAs into a single assembly module (increased form, fit, and function through added capability within the same footprint).

All components, both actives and passives, were imbedded into cavities (Z direction) in the laminate substrate. Multiple tiers were exposed in the substrate with strategic placement of components to decrease interconnect length (component-to-component bonding and component-to-substrate bonding) and address power dissipation. Bonding high-power devices with thermally conductive adhesive directly to an imbedded thermal core in the substrate eliminates the need for external heat sinks and lowers the devices’ junction temperature.9

Flexible aluminum wire bonds (Figure 5) were used to electrically interconnect the devices (component-to-component for point-to-point) and circuit (component-to-substrate for multi-point nodes). These flexible interconnects are able to absorb the thermal and mechanical stresses created when operating in harsh environments. Elimination of secondary packaging, which facilitates bonding from component-to-component, also decreases the number of failure opportunities in the system.

|

| Figure 5. Wire bonds to electrically interconnect components on the prototype. |

The prototype was analyzed and tested by SM-2 prime contractor Raytheon Missile Systems, which approved the prototype as flight hardware for a flight test. This included finite element analysis (FEA) design modeling and prototype qualification testing per standard legacy performance requirements and overstress test requirements (e.g. temperature, humidity, vibration testing). In October 2007, the prototype’s performance and robustness were demonstrated through a successful SM-2 flight test. The imbedded product was given TRL 8 status, meaning that the technology has been proven to work in its final form and under expected conditions. Examples include developmental test and evaluation of the system in its intended weapon system to determine if it meets design specifications.10

Materials Analysis

Materials analysis was performed on the prototype to determine the effects of performance qualification and overstress testing on the prototype units. A cavity was removed from the prototype to perform surface and micro-section analysis of the physical (die attach and conformal coat) and electrical (bond wires) interconnects. Prior to surface analysis, an aggressive organic solvent removed the encapsulant from the cavity to enable visual analysis of the various surfaces (through the conformal coating).

A scanning electron microscope (SEM) exposed the component/substrate topology and wire interfaces. The backscattered electron imaging mode provided a high-magnification grayscale digital image of the device (Figure 6 and Figure 7). At high magnification, the substrate bond interfaces and die bond interfaces were inspected for signs of fatigue and stress fractures. However, the conformal coating remained over the die and wire surfaces, creating a monochromatic image around the components, bond wires, and substrate. Within this cavity, multiple component geometries and wire profiles are represented as well as multi-tier component placement (cavity within a cavity).

|

| Figure 6. Micrograph SEM image (fisheye mode) of cavity with imbedded components and bond wires. |

|

| Figure 7. Micrograph SEM image of cavity-within-a-cavity (to thermal core) with imbedded components and bond wires. |

The cavity was then micro-sectioned to analyze component-to-substrate interfaces and bond wire interfaces. The component-to-substrate interface directly affects physical attachment of the device to the substrate (and also electrical connects IC bulk silicon potentials to the corresponding voltage, as required) and is critical to withstanding cyclic thermal stress and shock/vibration. The bond wire interfaces are paramount to function and performance of the circuit where any stress fractures or lifts directly affect contact resistance and can lead to high resistance connections (open).

The component-to-substrate interface (Figure 8) is continually stressed due to the significant difference in CTE of the substrate bond pad (laminate = 16-20ppm/°C, copper = 16 ppm/°C, and aluminum = 24 ppm/°C) and the low CTE of electrical devices (ICs: silicon = 3 ppm/°C, Passives: ceramics = ~6 ppm/°C). Many parameters should be considered in calculating the induced stress (per Hooke’s Law) in a component-to-substrate interface. A designer has little control over certain parameters (component CTE, ΔT, dimensional parameters), but proper selection of the die attach adhesive (modulus, CTE, Tg) can significantly reduce interfacial stresses. Micro-section analysis of one such interface revealed no delamination (separation of materials) or stress fractures between the component-to-die attach interface or substrate-to-die attach adhesive interface.

|

| Figure 8. SEM micrograph of component-to-substrate interface with thin bond line thickness to decrease thermal resistance. |

The bond wire interface (Figure 9) is also affected by CTE differences in substrate and component bond pad materials (thermal stress), in addition to use environment stresses such as vibration and shock. The use of flexible interconnects, such as aluminum/1%silicon wire, prevent stress fractures in the electrical connect due to expansion and contraction of the devices and substrate during cyclic temperature changes. However, repeated wire flexing (such as during multiple thermal shock cycles) can lead to failures. Preventive measures such as conformal coatings and encapsulants and bond parameters (such as loop height) can prevent failures related to thermal expansion.

|

| Figure 9. SEM micrograph of a silicon die bond pad-to-wire (Al/1%Si) interface. |

These preventive materials and process parameters also aid in eliminating wire failures due to vibration and shock. Low-stress encapsulants act as a shock absorber to reduce the amount of force transferred to the wire when exposed to mechanical shock and vibration. Reduced wire lengths and controlled loop heights (Figures 10 and 11) also prevent fatigue and breaking by altering the resonant frequency of the wire bond.11

|

| Figure 10. SEM micrograph a low-profile bond wire (step down from die to substrate) with first bond on the die surface. No lifts or fatigue cracks along the interface. |

|

|

Figure 11. SEM micrograph a low-profile bond wire (step down from die to substrate) with second bond on the substrate. No lifts or fatigue cracks along the interface.

|

Wire bonding electrical interconnects versus conventional processes such as soldering provides significant flexibility in interconnecting miniaturized components in odd form factor packages where access to create these interconnects is restricted. High power devices located in recessed cavities for improved heat transfer (bonded to an imbedded cooling core) limit access to the die surface. Configurable bonding parameters enable access to the die bond pads in these locations (Figure 12).

|

| Figure 12. SEM micrograph of a die bonded to the thermal core (deep access) in a recessed cavity. No lifts or fatigue cracks along the interface. |

Like any metallurgical interface, intermetallic compounds are formed and are subject to failure. For bond wire interfaces, the classical failure mode is Kirkendall voiding which is often referred to as the “purple plague”. The failure mode is a function of several parameters: metallurgical interfaces (wire and pad metal composition), metal impurities, ion diffusion rates (aluminum diffuses more rapidly into gold), and environment (time and temperature). The term “purple plague” is derived from the characteristic color of one of the five intermetallic compounds that is formed at high temperatures (above 150°C) over time in gold/aluminum (Au/Al) compounds (such as Au ball bond to Al bond pad). The intermetallic layers are more brittle than either Al or Au and are prone to crack during temperature cycles or stresses. Therefore, the room temperature wire bonding process using ultrasonic wedge bonds (Al/1%Si wire) is preferred due to the bonding method (ultrasonic bonding is room temp versus high temp thermosonic bonding) and metallurgical interfaces (die bond pad-to-wire: Al-Al and passive bond pad-to-wire: Au/Al).11 Due to the overstress testing performed on this prototype, bond interfaces were inspected at high magnification for indication of fatigue cracks at the Au/Al interfaces (Figure 13). No voids or fatigue cracks were detected in the Au/Al interfaces, e.g. passive end termination-to-wire or substrate bond pad-to-wire.

|

| Figure 13. SEM micrograph a gold-plated capacitor end termination bond wire. No voids or fatigue cracks were detected along the interface. |

Conclusion

The testing of the two test vehicles has demonstrated that imbedding components and die is a robust packaging technology for use in products that must operate in harsh environments. The two test vehicles discussed in this paper have proven that the design guidelines, materials, and process parameters used to manufacture imbedded package assemblies are capable of withstanding temperature, humidity, and shock stresses. Test Vehicle 1 (daisy-chain sample) survived over 3000 cycles of thermal shock exposure before a failure occurred. Test Vehicle 2 (mixed-signal prototype) was bench tested to meet and exceed legacy product performance specifications in order to qualify the prototypes as flight hardware. Lastly, a successful flight test in October of 2007 was paramount in demonstrating imbedded component packaging technologies’ ability to meet form, fit, and function requirements in a miniaturized robust package.

*The packaging technology described here is registered by STI as Imbedded Component/Die Technology (IC/DT).4

ACKNOWLEDGEMENTS

The findings of this study could not have been accomplished without the support of the STI Microelectronics Lab and the STI Analytical Lab under the direction of Mark McMeen. The author would like to acknowledge the efforts of Jonnie Johnson and David Robinson for support of the design, assembly, and test of the prototype assemblies as well as Aaron Olson and Bryan McMeen for the post-stress testing sample preparation and analysis.

REFERENCES

1. Greig, Bill, “New and Emerging Technologies,” Advanced Packaging, July 2002.

2. Cooper, C. and McMeen, M., “Effects of Process Parameters on the Material Characteristics of Die Attach Adhesives,” Pan Pacific Microelectronics Symposium, January 2007.

3. Hatcher, Casey, “Imbedded Component/Die Technology: An Innovative Packaging Solution for High Reliability,” Pan Pacific Microelectronics Symposium, February 2004.

4. Raby et al. "Imbedded component integrated circuit assembly and method of making same." U.S. Patent 7,116,557. 3 October 2006.

5. Naito, C. and Todd, M., “The effects of curing parameters on the properties development of an epoxy encapsulant material,” Microelectronics Reliability, Vol. 42(1), pp. 119-125, 2002.

6. Gilleo, K., “Introduction to Material Science: Polymers and Fillers,” W-25: Conductive Adhesives Workshop – APEX Conference, March 2003.

7. Wong, C.P. “Polymers for encapsulation: Materials Processes and Reliability,” Chip Scale Review, March 1998.

8. Virmani, N.V. and Shaw, J., “Critical Concerns, Solutions and Guidelines for Use of Plastic Encapsulated Microcircuits for Space Flight Applications,” Retrieved October 4, 2006, from the NASA, Technology Validation Assurance Web Site: http://misspiggy.gsfc.nasa.gov/tva/pems/esapems.htm

9. Santarini, Michael, “Thermal Integrity: A Must for Low-Power-IC Digital Design”, EDN, September 2005.

10. “Appendix B: Technology Readiness Level (TRL) Descriptions”, NASA SBIR Website: http://sbir.nasa.gov/SBIR/sbirsttr2007/solicitation/appendix_B.pdf

11. Harman, George, “Wire Bonding in Microelectronics: Materials, Processes, Reliability, and Yield,” New York, NY: McGraw Hill, 1997.

Casey H. Cooper, STI Electronics Inc., Madison, AL, may be contacted at [email protected].

Advanced Packaging, April 2010