By Debra Vogler, senior technical editor

March 31, 2011 — Serial entrepreneur, Zvi Or-Bach, was interviewed by ElectroIQ about his latest startup, MonolithIC 3D. In this podcast interview, Or-Bach explains why the company changed its name (from NuPGA) when its mission changed. "The name change was in response to a strategic change we made once we discovered a path to monolithic 3D ICs," said Or-Bach. He noted that on-chip interconnects are the limiting aspect with respect to scaling, and that after making materials changes (i.e., Al to Cu, and SiO2 to low-k), the only solution is to go to 3D ICs.

Listen to Or-Bach’s interview: Download (iPod/iPhone users) or Play Now

| Interconnect delay → Monolithic 3D | Implant H+ dummy gates | Transfer on top of processed wafer and replace gates (<400°C) | |||||||||||||||||||||

|

3D → |

||||||||||||||||||||||

|

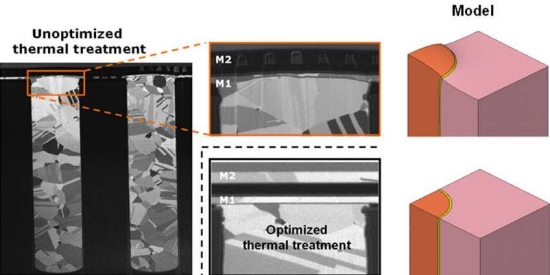

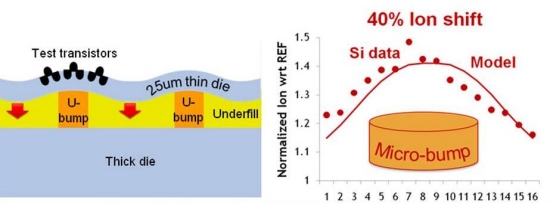

Figure. Next-generation monolithic 3D IC — leveraging the gate-last process. SOURCE: MonolithIC 3D |

|||||||||||||||||||||||

Semiconductor scaling costs

| Scaling down 0.7x | Scaling up (3D packaging) | |||||

| Cost: | Capital >$4B | Cost: | Capital: <$200M | |||

| R&D >$1B | R&D <$100M | |||||

| Benefits: | Die size 0.5x | Benefits: | Die size 0.5x | |||

| Power 0.5x | Power 0.5x | |||||

| Speed: | No change | Speed: | No change | |||

|

Table. The next-generation dilemma — going up or going down? Companies can do both. SOURCE: MonolithIC 3D. |

||||||

"While TSVs are a big help with off-chip interconnects, they are not helpful for on-chip interconnects — they are just too large," explained Or-Bach. "Our vertical interconnect is 10000× more dense than TSVs." The company’s mission is an answer to what Or-Bach calls the next-generation dilemma (table). Whether one chooses to continue to scale down 0.7×, or scale "up" by going to 3D, there are costs. However, the company’s estimates show a glaring difference: capital costs and R&D costs are, respectively, >$4B and >$1B for scaling down; and <$200M and <$100M for scaling up.

3D IC technology

The technology being proposed by Or-Bach uses a combination of four ideas:

1) the gate-last process and proper sequencing of ion-cut (i.e., Smart Cut) technology;

2) low-temperature face-up layer transfer;

3) repeating layouts;

4) innovative alignment.

Or-Bach explains the process in detail (figure) in his audio interview. The technology still requires process development work, but looking ahead, Or-Bach views it as being applicable to both Tier 2 fabs that want to reinvent themselves and compete with leading-edge fabs, and leading-edge fabs that want to add value.

Subscribe to Solid State Technology/Advanced Packaging.

Follow Advanced Packaging on Twitter.com by clicking www.twitter.com/advpackaging. Or join our Facebook group