|

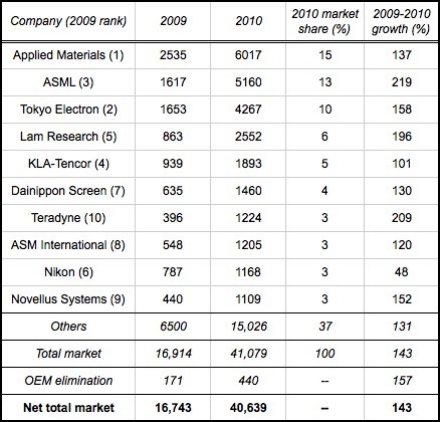

Executive Overview

The cleaning process performance in both conventional wet-bath and a single-wafer processor was evaluated. Experiments performed in this study were primarily oriented toward the determination of the number of particles added onto the wafer by using various pumping methods. In particular, the impact of pump-induced particles on silicon wafer cleaning in DI water was investigated. The random yield of ICs was estimated from the particle count data using various correlations including a negative binomial model.

|

R. Prasanna Venkatesh, Jung-Soo Lim, Jin-Goo Park, Hanyang University, Ansan, Korea

Particle contamination in the microelectronic fabrication process must be below the threshold limit, i.e., <100 each [1], otherwise it would eventually result in yield loss. It is reported in the literature that 75% of total yield loss is coming from particle contamination during manufacturing steps [2], hence this issue has been drawing much attention in recent years. However, to our knowledge, there is no experimental evidence on the effect of pumping methods on particle contamination on the wafer during the cleaning step. Therefore, in this study, the performance of the magnetic levitation centrifugal pump (MLC-BPS 600, Levitronix) during the cleaning operation is evaluated and compared with traditional diaphragm pumps (D1 and D2) in terms of particles added onto the wafer.

Recirculation of DI water was carried out for 24 hours and the recirculated DI water was exposed to 8" bare silicon wafers in both a conventional wet-bath tool, and a single-wafer cleaning processor (Goldfinger, Akrion, USA). Wafers were exposed to the cleaning system at the end of every four hours for the typical process time of 10 minutes and 30 seconds in the conventional wet-bath, and single-wafer processor, respectively. The number of particles on the wafer was measured using a laser surface particle scanner (ST 6600, KLA-Tencor, USA). Experiments were conducted at different flow rates (15 and 10 lpm) for a single pressure of 30psi in a conventional wet bath tool. In the single tool, the flow rate was kept at the maximum value of each pump: 20 lpm for the MLC pump, and 15 lpm for both the D1 and D2 pumps.

Pump-induced particle contamination

The effect of pumping methods on the number of particles added onto the wafer during the 24-hour cleaning test in the wet bath is shown in Fig. 1 (a-c). In the case of the BPS-600 pump, the total number of added particles on the wafer is below 5000 at all the flow rates. In the case of both the D1 and D2 pumps, the particle count on the wafer goes beyond the detection range of the instrument. The maximum measuring capability of the laser surface scanner is 30,000 particles. If the wafer has particles that are beyond the instrument inspection limit, then it could not detect the total number of particles and displays the error message. In that case, the number of particles on the wafer would be more than 30,000. In both of these diaphragm pumps, the total number of added particles on the wafer increases with flow rate as shown in Fig. 1 (b-c). This behavior is more common in pumps as the particle shedding from the pumping system increases with the increase in flow rate [3]. However, in the case of the BPS-600, the opposite behavior is observed, i.e., the number of particles is more for the lower flow rate especially after 12 hours of circulation. The reason for this behavior is not yet clear.

|

|

Fig. 1: Particle count on the wafer as a function of circulation time in a wet bath tool for a) MLC pump, b) D1 pump, and c) D2 pump.

|

The effect of pumping methods on the number of particles added onto the wafer during a 24 hour cleaning test in a single-wafer processor is shown in Fig. 2. In the MLC pump, the total number of particles added onto the wafer is much less (i.e., ~300) and there is no significant change in the number with circulation time. The trend looks similar with the D2 pump, though the number of particles (500) is slightly higher. However, the particle count slightly increases with circulation time especially after 12 hours. In the case of the D1 pump, the wafer particle count is relatively higher (4200 at the 24th hour) and increases linearly with circulation time. The particle number is significantly lower in this test compared to that of the test carried out in the wet bath because of the lower process time.

|

| Fig. 2: Particle count on the wafer as a function of circulation time in a single wafer processor tool. |

From the cleaning studies performed in both conventional wet-bath and single processor, it can be concluded that the number of particles generated by the BPS-600 pump is lower than the number generated by either of the diaphragm pumps. Closer examination of the particle size distribution shows that the number of particles generated by all three pumps is in the range of 0.173-0.326µm, which is in the critical regime that results in yield loss of ICs as reported in the literature [2]. In the following section, the chip yield is calculated using the particle count data.

Chip yield calculation

The addition of particles on the wafer during chemical and DI rinses would be critical to reduce the device yield. The yield loss due to the particle contamination is calculated by correlating the number of particles in ultra pure water (NB)) to the defect density (DO) [4]:

DO = NBSKRPD,

where S is the amount of ultra pure water that contacts the wafer during the fabrication step; KR is the fraction of killing particles, and PD is the probability of particles deposited onto critical areas. For the given process step, the product of SKRPD is constant. Similarly, the other study shows there is a linear correlation between the number of particles in the wet bath (NB) and on the wafer (NW) [5], i.e., NB = ANW.

The value of constant A is also the same for all the pumps if we assume the composition of particles generated by all three tested pumps is the same. Using the above two equations, the ratio of defect density of the two pumps is given by the ratio of the number of particles added onto the wafer.

Then, yield (Y) can be calculated from the defect density using the following negative binomial model [1].

Where Ac is the critical area of the chip and C is a clustering factor. One could estimate the yield variation for different hours of recirculation for different pumps if those values are known. For ready comparison, the chip yield is simulated for all three pumps by assuming the values for DO, MLP =1; C=2 and AC= 0 to 10 cm-2 ; the results are plotted in Fig. 3 and Fig. 4 for both conventional wet-bath and single processor, respectively. The data clearly show that there is a significant difference in the chip yield between the MLC pump and the traditional diaphragm pumps in both cleaning cases.

|

|

Fig. 3: Simulated chip yield as a function of critical area for all the three tested pumps. The pump flow rate = 15 lpm; recirculation time = 24hrs.

|

|

|

Fig. 4: Simulated chip yield as a function of critical area for all the three tested pumps. The recirculation time = 24hrs.

|

Conclusion

The cleaning studies of silicon wafers in DI water in both conventional wet-bath and a single-wafer cleaning tool clearly show that the pumping methods have a strong influence on process performance. Particle contamination on the wafer is lower during pumping with the MLC pump than the traditional diaphragm pumps and consequently, it resulted in a decrease in the yield loss of the ICs. It is therefore critical to choose the right pump for circulating DI water and chemicals during the wafer-cleaning process.

References

1. http://www.itrs.net/Links/2000UpdateFinal/FrontEndProcesses2000final.pdf

2 J.D. Plummer, M.D. Deal, P.B. Griffin. Silicon VLSI Technology – Fundamentals, Practise and Modeling, p. 151, Prentice Hall, New Jersey (2000).

3. M.R. Litchy, R. Schoeb, "Critical Components and Subsystems," Semiconductor Fabtech, 38, 89 (2009).

4. F. Wali, D. M. Knotter, A. Mud, F. G. Kuper, Microelectronic Engineering, 86, 140 (2000).

5. L.W. Shive, K. Ruth, P. Schmidt, Micro: Extreme Silicon part, 1, Feb (1999).

Biographies

R. Prasanna Venkatesh received a bachelors’ degree in chemical engineering from Bharathidasan U., India, and a masters’ degree in petroleum refining and petrochemicals from Anna U., India; he received his PhD in chemical engineering from the Indian Institute of Technology Madras, India and is currently a post-doctoral candidate at Hanyang U., Ansan, 426-791, Korea.

Jung-Soo Lim received his BS in chemical engineering and MS in metallurgy and materials engineering from Hanyang U., Korea, and is a PhD candidate at the university.

Jin-Goo Park received a BS in metallurgy and materials engineering from Hanyang U., Korea, and MS and PhD degrees in materials science and engineering from the U. of Arizona. He is a professor in the Department of Materials Engineering as well as director of the Micro Biochip Center and the Nano-bio Electronic Materials and Processing Lab. (NEMPL), at Hangyang U.; ph.:82-31-400-5226; email [email protected]

More Solid State Technology Current Issue Articles

More Solid State Technology Archives Issue Articles