(September 20, 2010) — Some challenging process conditions encountered in volume package production require die-attach coatings as thin as 38µm to be applied to wafers that have been mechanically thinned to as little as 150µm. With such thin wafers, and the requirement for low coating thickness, the wafer-support tooling surface metrology should have an appreciable impact on coating thickness control. Thinner wafers may more easily translate deviations through their more flexible structure. Jeff Schake, Mark Whitmore, Dave Foggie, Michael Brown, DEK Printing Machines Ltd., discuss the flatness characteristics of available wafer pallets, and describe an experiment to measure and compare the process performance achieved when depositing a B-stage adhesive onto a total sample of 45 150µm-thick, 200mm wafers, using six pallet types.

Applications for wafer print coating include protective coating and die attach adhesive applied on the backside, and non-capillary active component protection on the front side. Standard metal stencils are often preferred, to achieve a smooth coating surface finish and ensure compatibility across a wider range of material rheologies than is typically possible using emulsion screens.

Highly uniform coating is always required; established processes are able to achieve nominal coating thickness of 50µm, with less than ±12.5µm total variation, on 200mm wafers of standard thickness (725µm). However, some of the more challenging process conditions now being encountered in volume production require die-attach coatings as thin as 38µm to be applied to wafers that have been mechanically thinned to as little as 150µm.

With such thin wafers, and the requirement for low coating thickness, the wafer-support tooling surface metrology is expected to have an appreciable impact on coating thickness control. The greater stiffness characteristic of thicker wafers may more effectively mask imperfections in the pallet surface caused by roughness, warpage, or debris on the pallet surface. Thinner wafers, on the other hand, may more easily translate these deviations through their more flexible structure.

Wafer pallet flatness

A key component to facilitate wafer stencil printing is the support tooling design. Support tooling secures and protects the silicon while holding the wafer in position for optimal balanced contact against the bottom of the stencil during processing.

Vacuum capability is an integral part to chuck functionality. A vacuum source inside the printer is linked to connection ports on the underside of the pallet, which allow suction to be delivered to the topside surface and distributed across machined V-groove channels or through porous cores. Vacuum pulls the wafer down flat against the pallet surface and also holds in place the stainless steel shim. This shim has thickness matching that of the wafer, and surrounds the wafer to provide stencil and squeegee support.

The manufacturing tolerances associated with base pallet construction will inevitably produce a surface that is undulating, not perfectly flat. A measure of the pallet flatness is usually obtained by recording the difference between highest and lowest “Z,” or vertical, measurement points.

Thin wafers may easily conform to such non-flat surfaces, upsetting print coating thickness uniformity. Elevation peaks occurring on the vacuum pallet surface will raise the thin silicon wafer in those areas, which reduces the space between the passing squeegee blade and wafer. Printed coatings in these local regions tend to be thinner as a result. This effect is reversed for areas on the pallet exhibiting depressions where the vacuumed wafer is pulled lower, increasing the space available to print coating material between wafer and squeegee.

Table 1. Stencil topside view during print coating process.

|

Pallet

|

Flatness (µm)

|

Mass (kg)

|

Size (mm)

|

Description

|

|

A

|

35 (200mm dia)

72 (300mm dia)

|

1.5

|

400 x 400 x 12

|

Weight-reduced Al with non-optimized reinforcement, circumferential, V-groove vacuum.

|

|

B

|

5 (200mm dia)

10 (300mm dia)

|

8

|

400 x 400 x 20

|

Solid Al, circumferential V-groove vacuum.

|

|

C

|

4 (200mm dia)

7 (300mm dia)

|

8

|

400 x 370 x 23

|

Solid Al, sintered stainless steel porous vacuum inserts.

|

|

D

|

17 (200mm dia)

33 (300mm dia)

|

3

|

400 x 400 x 20

|

Weight-reduced Al with optimized reinforcement, circumferential, V-groove vacuum.

|

|

E

|

8 (200mm dia)

10 (300mm dia)

|

4.5

|

400 x 400 x 12

|

Weight-reduced steel, circumferential V-groove vacuum.

|

|

F*

|

4 (200mm dia)

8 (300mm dia)

|

10

|

400 x 400 x 20

|

Solid stainless steel, ceramic porous vacuum insert.

|

|

* Flatness values are predicted, not measured.

|

A number of suppliers offer wafer chucks for use in coating processes. Table 1 compares the construction, vacuum design, and surface flatness characteristics of a variety of pallets available from commercial producers. The pallets assessed span a range from low-cost and lightweight units to high-precision solid-stainless-steel pallets, with various vacuum mechanisms.

Generally, a lightweight pallet is considered more suitable for automatic transport on a standard printing machine. However, heavier pallets tend to have better flatness control.

Wafer coating experiment

Using each of the pallets described in Table 1 to coat wafers of 200mm diameter and 150µm thickness with a commercial B-stage die-attach adhesive, using a 38µm stencil, the effect of pallet performance on coating thickness variation can be quantified. The results aid selection of suitable wafer-support tooling, and inform process optimization and maintenance for high-volume wafer-coating processes at leading-edge wafer-level package geometries. An additional 12 wafers of standard 725µm thickness were also included as a benchmark to compare coating thickness uniformity trends against thinner wafers. These were printed using pallet A only. The material used for stencil print coating was a nonconductive wafer-applied die-attach adhesive. Some of the key adhesive characteristics are listed in Table 2.

Table 2. Print material properties.

| Function |

WL die attach |

| Viscosity |

42,000cps |

| Specific gravity |

1.5g/cc |

| Color |

Yellow |

| Conductive |

No |

| B-stage capable |

Yes |

| Snap cure capable |

Yes |

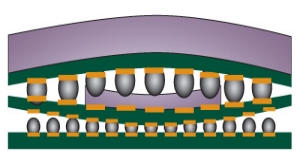

In a production wafer-coating process (Fig. 1), the pallet (with wafer) is conveyed into the printing machine and clamped in place under the stencil. A moving camera then locates fiducials on the shim and under the stencil. Automatic stencil position correction then aligns the aperture opening with the wafer. The pallet is lifted the minimum distance required to make firm contact against the stencil, without displacing it, and then squeegee pressure is applied down against the stencil. The squeegee is moved across the aperture to print the material.

|

| Figure 1. Stencil topside view during print coating process. |

At this stage, it is worth noting that high-performance pallets are typically too heavy for automatic transport on a standard printing machine. With this in mind, heavy pallets were used with a standard printing machine by loading the pallets into and out of the machine manually. In addition, a machine with a specialized heavy-duty conveyer rail transport system, termed heavy pallet rail (HPR), was used to test print results when automatically shuttling and printing heavy pallets.

The coated wafers were subsequently exposed to a B-stage cure profile to drive out the contained solvents without fully curing the material. Coating thickness measurements were then taken by removing small slices of printed material to expose the underlying silicon in a number of locations across the wafer surface.

Coating thickness measurement

To accurately measure coating thickness in each location, the uncovered silicon is used as a reference surface for a white-light interferometer. The instrument is then programmed to automatically step upwards to capture the profile of the coating surface. Figure 2 shows an example measurement; in this case the coating thickness reported is 25.0µm.

|

| Figure 2. Measuring coating thickness with an interferometer. |

Coating thickness was inspected at a minimum of 28 locations for each wafer, split across horizontal and vertical axes aligned through the center of the wafer (Fig. 3). Green labels represent wafer locations that avoid vacuum channels, while the red labels measure coating thickness at positions corresponding to vacuum channels (applies to pallets A, B, D, and E only). Pallet C is unique in that red labels represent measurements over porous/non-porous transition points. All pallet F measurements correspond to porous wafer support areas.

|

| Figure 3. Measurement locations for coating thickness on printed silicon wafers. Wafer notch position is down. |

Results

All wafer coating thickness measurements from the six pallets are compiled together and plotted in Fig. 4. The average thickness achieved is similar between pallets and processes, which was expected by design.

|

| Figure 4. Scatterplot of individual coating thickness measurements. |

Note that a thicker 50µm stencil was used with the standard-thickness wafers, and that the average coating thickness reported is quite similar to the results with the 38µm stencil. The average coating thickness can be adjusted by changing stencil thickness and print process settings. However, coating thickness uniformity is the more important metric when evaluating process performance.

Taking this into account, it is quite clear that test A3 is the worst overall result having the widest coating thickness distribution. Tests A1, A2, and A3 all use the same pallet design, which happens to measure the poorest in flatness control. It is interesting to compare the coating thickness trends between these three tests as A3 is the only one using thinner wafers with results giving a much larger thickness scatter in this data set. This supports the theory that thin wafers require flatter support pallets to produce uniform print coatings.

Pallet F data also shows some coating thickness distribution discrepancy, which has been highlighted in the graph by using two types of dark-blue diamond symbols; some are fully colored and others are only outlined. After completion of the experiment it was found that the wider thickness distribution indicated by the outlined diamonds correlates with a small amount of post-cleaning debris (a single strand of fiber) found on the pallet surface. The outlined diamonds show measurements believed to have been distorted by this debris. For the other four pallets (B, C, D, and E), the coating thickness uniformity appears fairly equal, making it more challenging to grade them in order of performance.

Another method of comparing thickness control is applied, to more easily identify performance ranking by presenting the data in the form of a capability ratio, or Cp. Mathematically, this is the process tolerance divided by six sigma. For this testing, the customary process tolerance of ±12.5µm was used, leading to the following equation for calculating Cp: Cp = 25µm/6 × standard deviation

It should be noted that there is some debate and confusion surrounding the use of the process capability index (Cpk), instead of Cp, to characterize the process performance. To clarify, the use of Cp in this analysis is based on measurement of print uniformity without concern to the actual thickness values measured. In other words, this testing is not designed to measure how accurate the print thickness can be relative to a specified target value, which is fundamental to a Cpk analysis.

|

| Figure 5. Print coating thickness Capability Ratio (Cp) comparisons. |

Figure 5 is generated by using the data from the subsequent thickness distribution scatter plot to calculate Cp values for each wafer. Higher Cp values indicate improved coating thickness control (i.e., lower standard deviation, less data scatter, more uniform distribution). A Cp value of at least 2.0 is required to establish 6-sigma process capability. As expected, test A3 produces the lowest Cp values, clearly demonstrating that pallet A is not suitable for printing 150µm-thick wafers. However, for the thicker 725µm wafers (tests A1, A2), pallet A is marginally acceptable since average Cp is close to 2.0.

Pallet F data is broken down into two components shown as both solid blue and outlined blue diamonds. Those measurements assumed to have been distorted by the fiber discovered on the pallet surface have been filtered out of the Cp calculations in the solid dark-blue diamond points. The difference between filtered and unfiltered Cp data confirms that the suspicious data contributes to the decline of process control. Pallet E is next worst in thickness control performance. This is somewhat surprising since measurement of the base pallet indicates good flatness.

Pallets B, C, D, and filtered F show good coating thickness control above the 2.0 Cp level. Of these, pallet C shows the highest average capability ratio and tightest Cp distribution. For this reason, pallets similar to type C, in terms of architecture and flatness, are recommended for supporting thin wafers in a stencil printing process.

Figure 5 also compares the standard machine’s performance with that of the HPR machine for both pallets C and F, designated by presence or absence of an asterisk in the x-axis label. It is difficult to be certain from this data that one type of machine is better performing, as pallet C prefers the HPR and pallet F favors the standard system. Therefore, it is reasonable to conclude at this point that the upgraded transport rails on the HPR machine do not impact print thickness control performance relative to the baseline printer.

Conclusion

To achieve proper wafer coating thickness control on thinner wafers, stricter tolerances on stencil printing variables are required. One such key variable has been identified as wafer support flatness. The pallet measuring the least amount of surface flatness variation in this experiment — pallet C — was shown to produce the most uniform printed wafer coatings. For 150µm-thick wafers, pallet flatness of 10µm or better is recommended. Thinner wafers may require even stricter flatness and/or vacuum design criteria.

One shortcoming of using ultra-flat pallets tends to be their excessive weight, which can limit automatic transportability on standard production tools. To address this, a new conveyer system for high-mass pallets has been developed and adapted to a standard stencil printing machine. This has successfully hosted a fully automatic wafer coating process delivering 6-sigma print thickness repeatability.

Although not a primary variable of interest in this study, the importance of cleanliness to the success of a stencil print coating process cannot be overemphasized. Contamination of the pallet F surface with a visible fiber did have a measurable negative impact on print coating thickness distribution. Although stencil printing at the wafer level can be successful in non clean-room environments, it is strongly advised to keep particle counts as low as possible since airborne elements can become trapped between the wafer and pallet, or under the stencil, or in the material itself. This noise variable, if unchecked, can contribute significantly to the decline of coating thickness uniformity.

Jeff Schake received his Masters in industrial engineering and dual Bachelor degrees in mechanical engineering and physics from Binghamton U. and is Senior Advanced Techonlogy Specialist at DEK USA Inc., 1785 Winnetka Circle, Rolling Meadows, IL, USA; ph.: +1 847 368 1155; [email protected].

Mark Whitmore has over 30 years experience in the electronics industry and is currently the Future Technologies Manager at DEK Printing Machines Ltd., Dorset, UK.

David Foggie has over 20 years experience in the electronics industry and is currently the Semiconductor Packaging Technologies Group Manager at DEK Printing Machines Ltd., Dorset, UK.

Michael Brown has HNC in mechatronics with over 14 years experience at DEK and is the SPT & AA Project Manager at DEK Printing Machines Ltd., Dorset, UK.

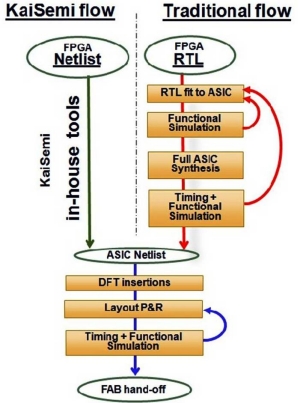

Backed by a tier-one fab vendor, KaiSemi’s automated conversion utilizes a database of multiple standard-cell fab process libraries. The wide range of libraries enables the conversion of any type and size of FPGA from any FPGA vendor to ASIC. This approach is accompanied by deep cost optimization during the automated conversion and allows the use of 3rd party standard hard cores (such as DDR interface, PCIe Phy, etc). The resulting ASICs — which are pin-compatible, timing-compatible, and functionally identical to the original FPGAs — consume less power and cost up to 70% less than their FPGA counterparts. Also read:

Backed by a tier-one fab vendor, KaiSemi’s automated conversion utilizes a database of multiple standard-cell fab process libraries. The wide range of libraries enables the conversion of any type and size of FPGA from any FPGA vendor to ASIC. This approach is accompanied by deep cost optimization during the automated conversion and allows the use of 3rd party standard hard cores (such as DDR interface, PCIe Phy, etc). The resulting ASICs — which are pin-compatible, timing-compatible, and functionally identical to the original FPGAs — consume less power and cost up to 70% less than their FPGA counterparts. Also read: