April 14, 2011 — E. Jan Vardaman, president and founder of TechSearch International, delivered a keynote address at the International Conference on Electronics Packaging (ICEP) held in Nara, Japan April 13-15. One of the key messages in her presentation was the trend toward the adoption of copper (Cu) pillar as highlighted in TechSearch International’s recent study, Flip Chip and WLP: Market Projections and New Developments.

Since Intel’s adoption of copper, many companies are moving to adopt copper pillar as the technology for their flip chip applications. Intel started with the use of copper pillar in its 65nm and 45nm flip chip product lines, and is using the technology in its 32nm products. The first products were the "Presler" and "Yonah" processors, but today Intel uses the copper pillar process in all of its flip chip products, including its Atom processor.

Cu pillar with a solder cap has also been used for GaAs and silicon in RF modules for several years. Amkor has been shipping RF Power Amplifier and RF front-end modules with Cu pillar bumps for more than four years. Drivers included size, performance, and cost.

Copper pillar is also shipping in leadframe packages from companies including Carsem and Unisem. IBM developed a copper pillar process called C2 that has been introduced for wire bond die with 50µm pitch or larger. TI has recently announced its use of Cu pillar in the bottom package of its package on package (PoP) offering.

Advantages of copper pillar, or copper post as it is sometimes called, were highlighted in TSMC’s recent technology day when TSMC presented its roadmap for the technology. Vardaman noted in her keynote that "the move to copper pillar is similar to the industry’s progression from the evaporated bump to the plated bump, and a major shift is expected in the 2013-14 timeframe."

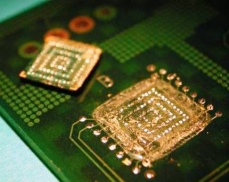

Highlighted in the ICEP presentation was STATS ChipPAC’s low-cost FC-CSP based on copper columns, bond-on-lead interconnection, and molded underfill. A 20-40% lower cost over standard flip chip packages for most designs has been reported. Several subcontract assembly operations offer molded underfill, including Amkor, ASE, and STATS ChipPAC.

The tremendous interest in copper pillar was evident at ICEP with a standing-room-only crowd listening to ASE’s presentation on its plans for Cu pillar in FC-CSPs.

TechSearch International Inc. is market research firm specializing in technology trends microelectronics packaging and assembly. Learn more at http://www.techsearchinc.com

Subscribe to Solid State Technology/Advanced Packaging.

Follow Advanced Packaging on Twitter.com by clicking www.twitter.com/advpackaging. Or join our Facebook group

Listen to Hsing’s interview:

Listen to Hsing’s interview:

The Q7000 Series has updated hardware and software, delivering a more tightly integrated assembly package, with approximately 30% fewer components and 50% less wiring than the Q2100 Series, which it replaces. These systems also cost less than the Q2100 models. The machines are designed with off-the-shelf components available directly from suppliers worldwide.

The Q7000 Series has updated hardware and software, delivering a more tightly integrated assembly package, with approximately 30% fewer components and 50% less wiring than the Q2100 Series, which it replaces. These systems also cost less than the Q2100 models. The machines are designed with off-the-shelf components available directly from suppliers worldwide.

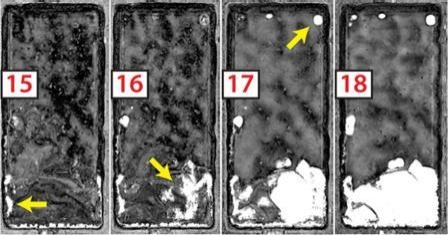

The iQ-200 simultaneously captures data from up to 12 J-type thermocouples, 16 air temperature/velocity sensors, and 4 differential pressure sensors to analyze

The iQ-200 simultaneously captures data from up to 12 J-type thermocouples, 16 air temperature/velocity sensors, and 4 differential pressure sensors to analyze