by Michael A. Fury, Techcet Group

January 18, 2011 – Day 3 of SMC 2011 started more quietly than days earlier in the week. There were fewer neckties, fewer jackets, more jeans — but still no Hawaiian muscle shirts.

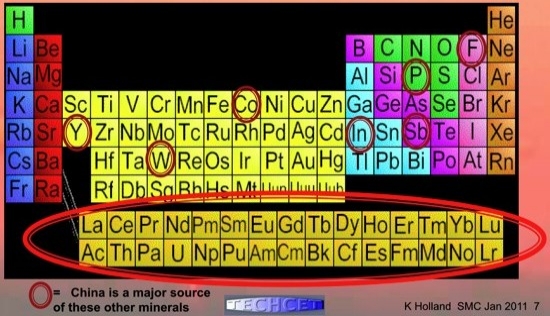

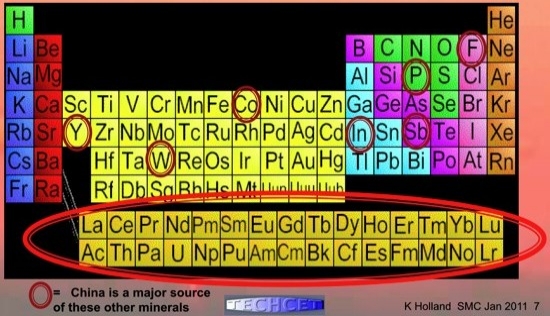

The materials analyst session led off with Karey Holland of Techcet Group. (‘Techcet’ is a palindrome of ‘tech’ forward and backward, but you all knew that by now, didn’t you?) The silica market is going gangbusters, and not because of CMP — it’s the increasing use of western-style toothpaste in China. There is no relief in sight for anxieties surrounding rare earth & other element supply constraints from China. Beyond rare earths, China’s mineral export restrictions are impacting WF6, phosphoric acid and HF supplies. Ta had been supplied mostly from the Congo, which is now prohibited as a ‘conflict mineral;’ the other main source in Australia had been shut down for not being economical. Funding lithography R&D for exposure tools and resist materials continues to challenge suppliers, particularly in light of still decreasing volumes of resist per wafer. There are still >9 players in resist and ancillaries; >20 players in CMP slurry, many continuing to gain market share, IP lawsuits notwithstanding.

|

| Rare earth elements are not so rare… |

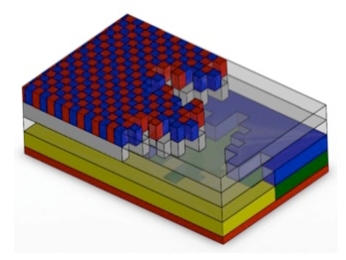

Continuing the materials and markets theme, Michael Corbett at Linx Consulting took a closer look at emerging materials in advanced devices. Did the ‘Decade of Materials’ (as declared by earlier SMC meetings) really begin in 2000? Based on SMC agendas, a decade ago, no one was talking about 450mm, PV, LEDs and 3D ICs. The materials market doubled from $20.3B in 2000 to $38.1B in 2010 (a 6.5% CAGR), with some of the largest growth in plastic substrates, bonding wires, CMP consumables and silicon wafers themselves.

Mike’s conclusion was Yes, it was, as evidenced by the entry of large chemical companies BASF, Dow and DuPont into the semiconductor side of the materials biz; and the successful introduction of high-k metal gates and litho alternatives. Low-k dielectrics was scored as a mixed bag, with successful implementation that is below expectations. The bifurcation of device and process types below 90nm continues to drive materials development demand.

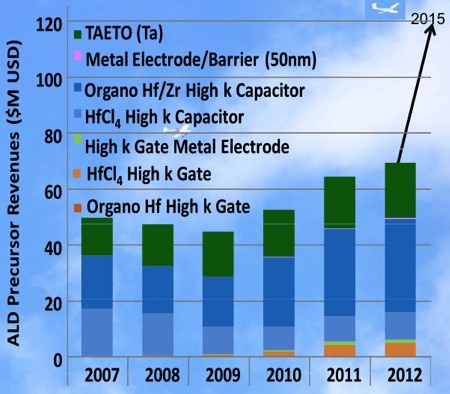

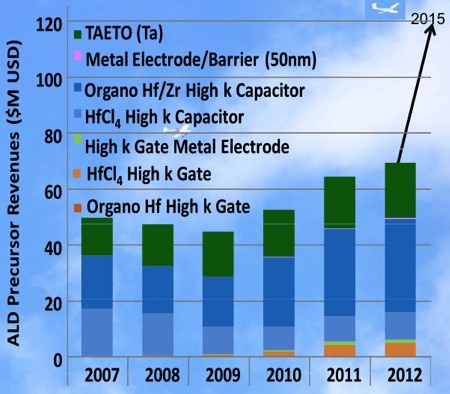

The ALD/CVD precursor market is expected to triple over the next five years. Adjacent markets have matured from being new target markets for suppliers to being competitors that can impact materials availability for semiconductors. These include PV, displays, and compound semiconductors; LEDs have not yet appeared on this radar.

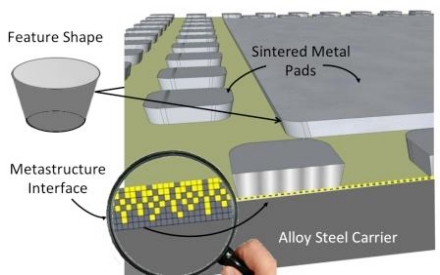

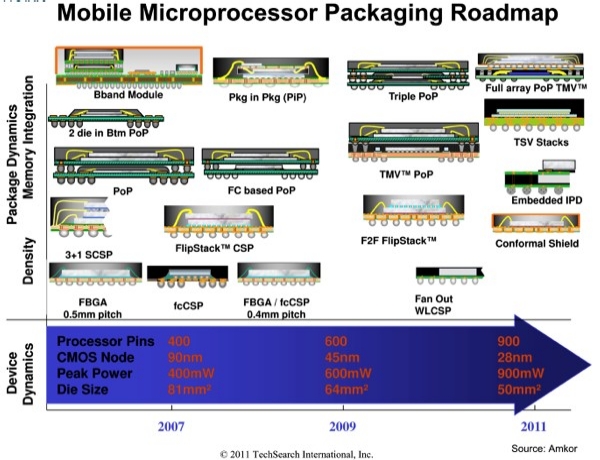

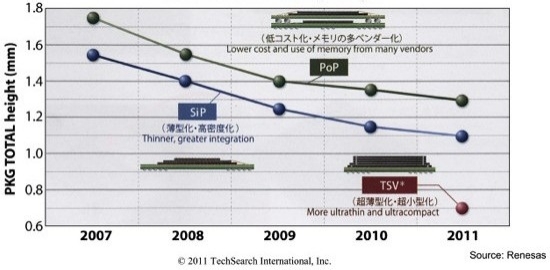

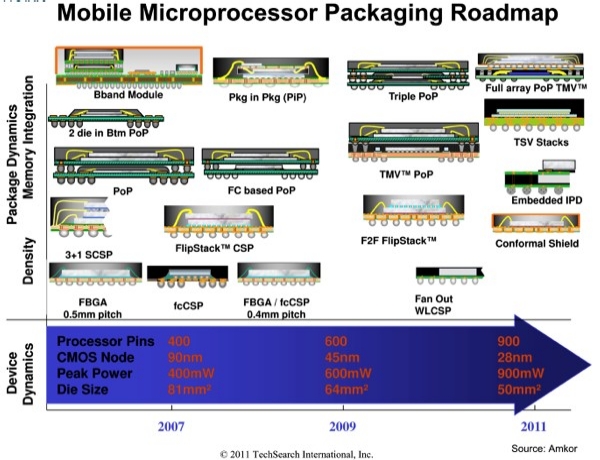

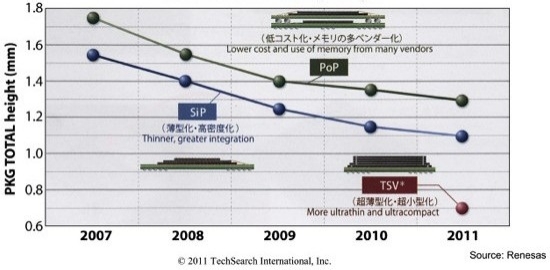

Defending the honor and value of semiconductor packaging materials, E. Jan Vardaman of TechSearch International launched a rapid-fire assault on a mountain of data — remember that the variety of packages is several orders of magnitude greater than the number of types of semiconductor devices. A trend from flip chip to wire bond began at 65nm. At the same time, by 2014 flip chip, WLP and Au bumps will account for 16% of IC shipments. Over the next 5 years, flip chip is projected to grow at 15%, with a shift to Cu pillar; WLP at 12.5%, with a shift from BCB to PI or PBO, and increasing use of fan-out. Nearly all smart phones use 3D package-on-package, giving this design a 27% CAGR. TSV implementation continues to be pushed out due to reliability data and supply chain infrastructure that still needs to be established for each device type. Jan put it succinctly: "TSV needs to move from PowerPoint to real engineering work." LEDs are going to drive a large set of packaging materials, many derived from existing supply chains, many not.

|

| Mobile microprocessor packaging roadmap. |

|

| Trend of stack SIP package height. |

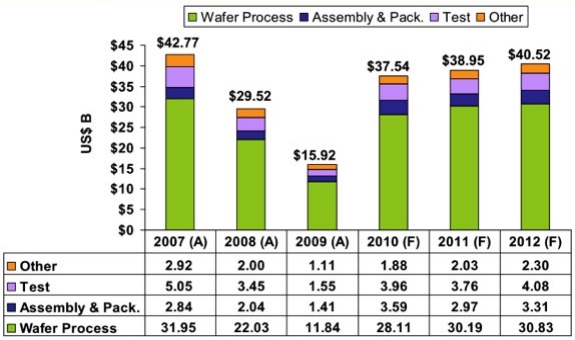

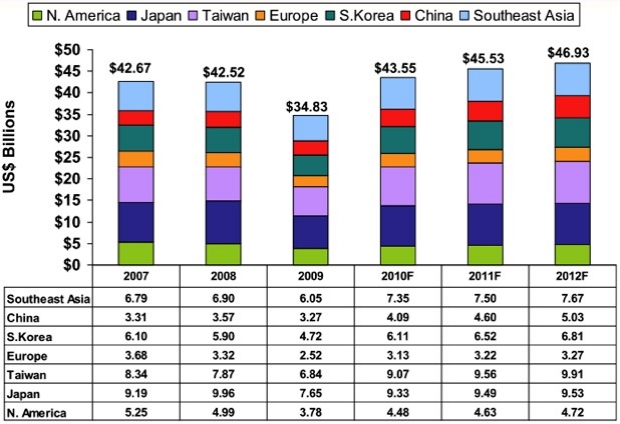

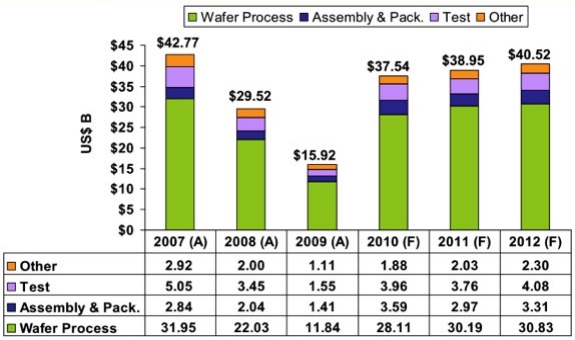

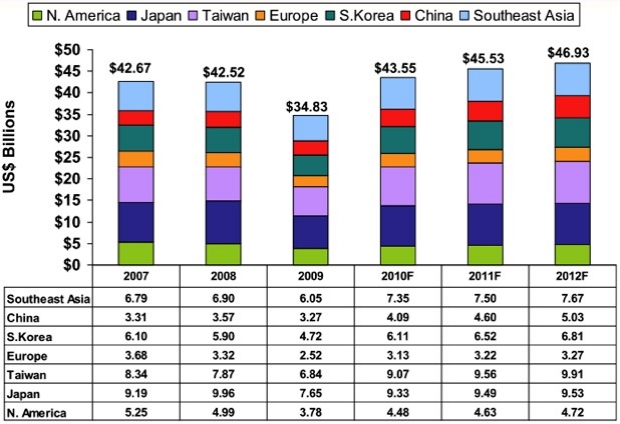

Dan Tracy of SEMI took a look at the industry and investment outlook. His overall materials revenue data for 2010 is $43.8B, while equipment is $37.5B. [Remember your basic calculus: equipment revenue tracks the first derivative of new capacity, and material revenue tracks the integral of the installed base.] Wafer shipments from Asia-Pacific are now >50% of total silicon area. Japan is still #1 in overall chip fab capacity, but they are #3 in 300mm capacity. Taiwan has passed the US to the #2 spot overall, followed by Korea, Europe, SE Asia and China. In packaging capacity, SE Asia and Taiwan lead, with China expected to pass Japan for #3 this year; Korea follows, with Europe & Americas trailing. Growth forecasts for 2011 are 6% for Si, 5%-6% for fab materials, and 3.5% for packaging.

|

2010 year-end equipment forecast by segment. Totals may not add due to rounding.

(Source: SEMI Year-end 2010 Semiconductor Consensus Forecast, Dec. 2010) |

|

| Materials forecast by market region. Totals may not add due to rounding. (Source: SEMI, Jan. 2011) |

A panel of these four speakers was moderated by Lita Shon-Roy of Techcet Group. Gold price escalation is driving an increased fervor for alternatives to wire bond. CMP steps will continue to be added as NAND overtakes DRAM. There is a collective of 1μm production volume that is poised to migrate to 0.25μm 200mm, which may sustain the demand for older material sets such as Al & Ti targets and W slurry. New capacity is still being added for 248nm resist. Supplementing Chinese rare earths with sea floor nodules is a possibility, but it’s more likely that as prices rise, new conventional mines will open or re-open outside of China. Supplier consolidation in front-end materials is slowing as the number of opportunities declines. Opportunities still exist in ALD precursors. Even though there are still ~20 slurry suppliers, they are now parts of larger companies. Packaging is still very active and the supplier base will continue to shrink. The trend to Cu wire bonds will take a huge chunk out of packaging revenues as Au is displaced. HKMG will collectively drive modest volumes of materials usage, but they are critical and will be extremely sensitive too supply constraints. The cost of Ru is likely to moderate its implementation and supply sensitivity. IP protection globally will more likely be improved by cultivating the appropriate company culture than by legal enforcement efforts. More Than Moore brings several new materials markets with it, but R&D funding strategies need to keep up with increasing costs and decreasing volumes per wafer.

The final speaker of SMC 2011 was Matt Gertken, Asia Pacific analyst for Stratfor (short for Strategic Forecasting), with a geopolitical perspective on what is happening in the world that affects our markets:

- US demographics are in relatively good shape compared to China, Japan, and Germany with respect to sustained GDP growth, due in large part to immigration. The US may need to maintain its presence in Iraq to mitigate movements by Iran, which is the region’s dominant conventional military power.

- The European debt crisis is exacerbated by southern European economies that traditionally rely on lower-tech and less sustainable industries.

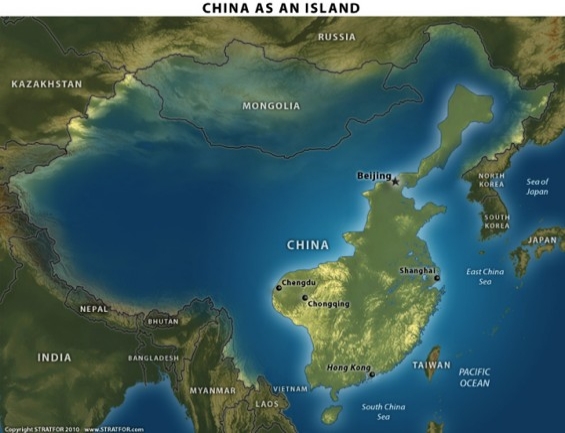

- China’s assertive foreign policy extends to accelerating resource acquisition, territorial disputes, and a huge investment in infrastructure in border areas. The Chinese restriction on rare earths closely followed a clash with the Japanese Coast Guard. The US has fully re-engaged in the AP region with new more balanced trade agreements. The Korean peninsula is destabilized by the impending succession of power in North Korea in 2012.

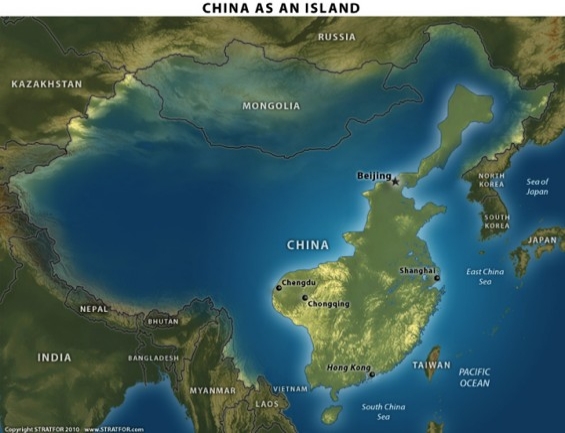

- One important angle to understanding dynamics within China: the vast majority of its population is limited to a number of regions, with the remainder of the territory very sparsely populated as a buffer area.

- Rising costs in China is leading to the collapse of several export businesses. China exports are already at the 10% global level, which is about where Japan topped out at its peak. Consumption is still <40% in China; US consumption at 70% is larger than Russia, China, Japan and Brazil combined. Fearing that growth would slow, China has unleashed a bank loan spree, increasing the level of unserviceable debt. This is the scenario that Japan experienced in the 1990s, with disastrous consequences.

- China is facing a generational change of leadership in 2012, both government and military. The current leadership has lacked the stature to anoint their own successors, which helped maintain stability in the past few transitions.

- China is holding more than $850B in US long-term treasury debt. However, the Chinese share of the US trade deficit is stable to shrinking, indicating some movement to improve the balance. Banks in China avoided the sub-prime collapse largely because home buying is highly capitalized with 40% down payments typical.

The next ISS & SMC meetings are scheduled for the week of January 15-20, 2012 returning to the Ritz-Carlton, Half Moon Bay, CA.

Michael A. Fury, Ph.D, is senior technology analyst at Techcet Group, LLC, P.O. Box 29, Del Mar, CA 92014; e-mail [email protected].

Listen to Chait’s interview: Download (for iPhone/iPod users) or Play Now