IMEC and its 3D integration partners have taped-out Etna, a new 3D chip integrating a commercial DRAM chip on top of a logic IC. The new 3D stack resembles as close as possible to future commercial chips. It consists of a 25µm thick logic die on top of which a commercial DRAM is stacked using through-silicon vias (TSVs) and micro-bumps.

Category Archives: 3D Integration

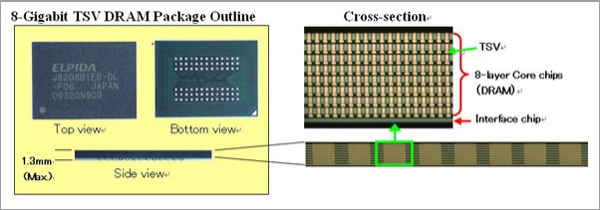

September 16, 2009 – Elpida Memory recently pushed vertical stacking of DRAM to new heights by connecting eight 1G chips using through-silicon vias (TSV), creating what it calls the world’s largest-capacity DRAM with ~8GB of storage.

The achievement doubles Korea’s Samsung Electronics stack of four chips, noted the Nikkei Business Daily. In the Elpida chip, each was etched with 1030 holes, using an internally developed method to position them with high precision and prevent distortions, the paper noted.

Reducing wire distance by connecting through the chip via TSV instead of with wire bonds enables faster speeds, lower power consumption (3/4 reduction in standby power vs. multichip/ packages and package-on-package), and smaller package size (1.3mm maximum, including an interface layer underneath). Future efforts may extend to multilayer TSV-enabled stacks combining logic and DRAM to create high-performance, low-power system chips, noted Elpida CTO Takao Adachi, in a statement.

|

| (Source: Elpida) |

A manufacturing line has been set up in Elpida’s Hiroshima plant, using Akita Elpida’s package processing technology, the company said; the Nikkei Business Daily pegged this as a ¥5B investment for a 10,000 wafers/month TSV line . Sample shipments are slated to start by year’s end, with 16Gb (eight-layers of 2Gb) sampling in mid-2010.

Vicky Wang, Henkel Loctite (China) Co. Ltd. and Dan Maslyk, Henkel Corp. show how underfill type and strategy will be key to enabling highly reliable PoP devices. Though many studies have investigated the board-level reliability of package-on-package (PoP) devices in relation to drop test and thermal cycling performance, packages manufactured with and without underfill and the impact of different underfill dispensing patterns (i.e., full underfill, cornerbond and edgebond), few studies have evaluated the effects of the underfilling strategy — such as underfilling the bottom component only or underfilling both top and bottom components — or the effects of solder alloy choice on the reliability of PoPs. This article presents findings from a recent study on the drop test reliability of PoP devices as a function of underfill dispensing type and PoP ball alloy type.

In this video interview from SEMICON West 2009, Bart Swinnen, reviews the established interconnect bonding and through-silicon via (TSV) technologies at the system-integration level. He also discusses the newer TSV possibilities and different application-specific TSVs.

Watch Bart Swinnen’s TSV and 3D interconnect interview here.

Karen Twillmann, executive director, corporate marketing, at Brewer Science, discusses the advances made by the company’s temporary bond adhesive for wafer bond applications:

Dan Wallace, director of 3D packaging at the company, told AP that it is in numerous development projects with end users. “At the same time we’re committed to the continuous improvement and introduction of 3D packaging solutions for the industry,” said Wallace. He noted that the company is focused on three key areas of focus relative to equipment, material and process, as related to temporary waferbond.

The current temporary adhesive, HT10.10, is rated at a 220°C maximum temperature tolerance, said Wallace. “Although in certain applications it can be exposed to much higher temperatures, conservatively we rate it at 220°C.” Recognizing that there is a need for adhesives that can withstand higher temperatures, the company is also engaged in development activity and is in the process to introduce materials capable of up to 300°C by the first quarter of 2010.

In a second area of focus, the company be will be introducing an R&D level high-temp slide debonder to support users who are not ready to invest in production-level equipment. “This will allow the flexibility to perform R&D activity in a confidential setting,” Wallace told AP. The Cee 1300DB has a planned introduction of December 2009 and information is available now.

A third area of focus is applications with solder bumps that require higher temperature tolerant adhesives >220°C. These materials will not tolerate the existing high temperature slide debond process. “We’re in proof of concept developing a patented room-temperature debond process combining the benefits of the thermoplastic adhesive while removing the need to debond at high temperature,” Wallace told AP. Alpha phase is targeted for 2Q10; “we are working with our partner EVG regarding automated equipment design and manufacture,” he said.

Karen Twillmann, executive director of corporate marketing at Brewer Science, discusses the advances made by the company’s temporary bond adhesive for wafer bond applications:

Dan Wallace, director of 3D packaging at the company, told SST that it is in numerous development projects with end users. “At the same time we’re committed to the continuous improvement and introduction of 3D packaging solutions for the industry,” said Wallace. He noted that the company is focused on three key areas of focus relative to equipment, material and process, as related to temporary waferbond.

The current temporary adhesive, HT10.10, is rated at a 220°C maximum temperature tolerance, said Wallace. “Although in certain applications it can be exposed to much higher temperatures, conservatively we rate it at 220°C.” Recognizing that there is a need for adhesives that can withstand higher temperatures, the company is also engaged in development activity and is in the process to introduce materials capable of up to 300°C by the first quarter of 2010.

In a second area of focus, the company be will be introducing an R&D level high-temp slide debonder to support users who are not ready to invest in production-level equipment. “This will allow the flexibility to perform R&D activity in a confidential setting,” Wallace told SST. The Cee 1300DB has a planned introduction of December 2009 and information is available now.

A third area of focus is applications with solder bumps that require higher temperature tolerant adhesives >220°C. These materials will not tolerate the existing high temperature slide debond process. “We’re in proof of concept developing a patented room-temperature debond process combining the benefits of the thermoplastic adhesive while removing the need to debond at high temperature,” Wallace told SST. Alpha phase is targeted for 2Q10; “we are working with our partner EVG regarding automated equipment design and manufacture,” he said.

Steven Dwyer, VP & GM, North America at EV Group, provides highlights of 3D integration papers the company presented at SEMICON West. By achieving alignment accuracy down to 200nm, thin wafer handling at thicknesses <10μm, and 300mm-capable wafer bonding, he says the company is ready for whatever comes along.

Larry Smith, Sr. Member of the Technical Staff, 3D Interconnect Division at SEMATECH, discusses the toolset acquisitions in progress at the University of Albany’s College of Nanoscale Science and Engineering. Researchers are focusing on 3D technologies that can replace traditional global interconnect and intermediate level processes, as well as on the manufacturing readiness of the toolsets.

Robert Rhoades, CTO, Entrepix, describes the nontraditional technology behind TFT-dual gate memory and how CMP enables that innovation among others (e.g., TSVs, 3D packaging, MEMS, and engineered substrates).

MCA’s BrightSpots 3D IC Forum came to a close on Friday, July 24. Out of 3 topic areas covering technology

progress, supply chain issues, and standards development, the discussions around technology progress were clearly the most active, both from a panelist and attendee perspective. What follows is a summary of each discussion. Where topics overlapped, and discussions were brief, the summaries have been

combined into one.

TECHNOLOGY PROGRESS AND LIMITATIONS

What is 3D IC’s position along the technology curve?

3D IC is progressing along the adoption and technology curve. All panelists agreed that it has moved

from the first phase of research into the early phases of commercialization, with pilot lines coming

online at manufacturing sites, and SEMATECH’s 3D interconnect program ramping up to take processes

beyond feasibility and qualify them as manufacturing processes. While skeptics remain, early adopters

such as Tezzaron Semiconductor will pave the way for volume production.

What problems does 3D solve in comparison to traditional scaling?

3D IC integration offers myriad solutions to problems over traditional scaling. According to Bob Patti of

Tezzaron Semiconductor, 3D IC with TSV interconnect offers increased speed and density for higher

performance at lower power and cost. He predicts that over the next decade or two 3D will take the

limelight from CMOS. “The exploitation of 3D has barely started,” he says. “The opportunities go far

beyond just connecting together the bond pads.”

However, because 3D requires new processes and design paradigms, it scares people. The industry has

20+ years of shrinking CMOS success, but it is becoming more difficult to achieve. Most people now see

3D as an option and the question is more of when is 3D going to be easier and/or cheaper. The key

challenge according to Michael Fritze of DARPA is getting folks to start thinking about the novel

architectures that would be capable of exploiting 3D IC benefits.

Once processes have been narrowed to a “manageable few”, with roadmaps and standards in place,

Sitaram Arkalgud of SEMATECH says 3D IC integration permits the cost-effective combination of

dissimilar materials, technologies and signals. He points out that when it comes to thermal dissipation,

lower power consumption of 3D stacks will result in less heat generated, and additionally the 3D

configurations lend themselves to new and innovative methods of dissipating what heat exists.

If nine-die stacks can be done with wire bonding, why go to TSV?

If required speed, performance and density can be achieved by interconnecting bond pads with wire

bond, then it’s the most cost effective way. For flash memory with low I/O count, there’s no motivation

to move to TSV stacking. However with DRAM, there is an “immediate need” for TSVs. CMOS

repartitioning requires it. Again, it all comes down to performance improvements and cost.

Along these same lines, other alternative technologies such as Vertical Circuits’ vertical interconnect

pillar process and 3D Plus’ wirefree die-on-die may offer similar advantages to flash memory, but again

when it comes to repartitioning, TSV is the only viable solution, according to our panelists.

What new capabilities are required of EDA tools to support 3D IC design?

Ric Borges reports work at Synopsys is ramping to provide tools in time for market adoption of 3D IC

integration. Design teams are establishing requirements and priorities as a step toward developing

roadmaps. He says 3D tools will be built on existing platforms.

In the meantime, start-ups like R3 Logic, MicroMagic and Javelin Design Automation have introduced

layout editors, pathfinding tools, etc. for designing 3D ICs, thereby fulfilling a critical role by providing

tools with which companies can determine the value of 3D IC technologies in different applications. It’s

a widely held understanding that these start-up companies have the flexibility to work with a new

technology before the market demand is there. If they succeed and the market develops, the larger

companies are likely to acquire them.

Additionally, Borges says Synopsys is addressing the need for simulation tools for some key areas of 3D

IC process development such as simulating the stresses generating in and around the TSV, detailed

modeling of deep trench etching and seed liner deposition inside the TSV, and design-oriented concern

of computing the TSV parasitic capacitance and resistance.

How should 3D ICs be tested, and what difficulties does this present?

With circuit-level 3D, device layer testing isn’t possible due to the number of interconnects per die

numbering in the millions. What Bob Patti recommends is a self-test and repair approach. He says

designers should be ready for a paradigm shift where future yield relies on how repairable and fault

tolerant your design is, rather than KGD. On the other hand, I/O level 3D interconnect will benefit from

work being done by probe testing companies developing contact-free probe technologies. There are

reportedly 2 or 3 groups working on this.

SUPPLY CHAIN ISSUES

Who will handle post-fab processes for 3D IC stacking?

While fabs are the most likely to handle TSV fabrication, there’s still question as to whether OSATS or a

third party will handle post-TSV processes including wafer backside processing, thinning, stacking and

bonding.

What business aspects need to be considered for volume production?

While companies with strong financial positions, experience, and track records are likely to be the most

suited to take on 3D integration, few exist (Toshiba and ST Micro come to mind) that have absorbed the

risk of investment thus far. Yole D