|

Executive Overview

The semiconductor industry is still in the early deployment phase of using high-k metal gates (HKMG) to overcome high leakage currents and higher power consumption of advanced devices. A particular challenge associated with implementing HKMGs is monitoring gate height. This article describes how picosecond ultrasonic technology can be used during various stages of process development, integration, and volume manufacturing for monitoring the HKMG stack.

|

J. Dai, P. Mukundhan, J. Chen, J. Tan, Rudolph Technologies, Flanders, NJ USA

D.B. Hsieh, T.C. Tsai, 1-United Microelectronics Corp., Tainan, Taiwan

High-k metal gates are a relatively new development in semiconductor manufacturing. Traditional gate architectures use polysilicon gate electrodes and silicon dioxide gate dielectrics, but these materials present difficulties at 45nm and below. Most notably, thinner gate oxides lead to high leakage currents, gate oxide breakdown, and dopant migration [1-2], creating untenable power consumption and reducing device reliability. High-k materials overcome these problems by enabling thicker gate dielectrics that reduce leakage current while maintaining high gate capacitance. Because the high-k materials are not compatible with polysilicon gate electrodes, a metal (typically aluminum) is used instead, hence the name high-k metal gate (HKMG).

Although at least one leading manufacturer is already in full production with advanced generation HKMG processes, the industry as a whole is still in the early deployment phase. The HKMG combination is important for all emerging applications that require high-performance and low gate-leakage, including all silicon and non-silicon nanoelectronic transistors (III-V materials, carbon nanotubes) [3]. It is being adopted by most IDMs and foundries due to its lower thermal budget, more stable threshold voltage, and better performance from strain-induced dummy gate removal than the alternative gate-first approach.

HKMG CMP process metrology

The gate height is critical to transistor performance and precisely controlling the gate height and uniformity is the primary challenge for the replacement metal gate aluminum CMP process. Non-uniform gate height can cause gate resistance variation, and improper gate heights can result in subsequent contact etch problems. Aluminum CMP is used to remove the Al overburden and work function metals from the field after Al gap fill. The gate height is only several hundred Angstroms, so the Al CMP process tolerance is much tighter than conventional CMP processes. This requires extremely tight within-wafer (WIW) and wafer-to-wafer (WTW) control of the Al polish for it is to meet gate height uniformity requirements.

Cross-sectional TEM (transmission electron microscopy) is often used to characterize gate height and thickness of work function metals during the research and development phase. X-ray reflectometry (XRR) has been used for thickness measurement on blanket wafers without the requirement for reference samples. However its accuracy strongly depends on modeling to adapt to graded layer, interface, roughness, and density, especially for thin films (a few hundred Angstroms). XRR also has an upper limit on thickness (< 3000Å) and cannot be used for pre-CMP Al measurements, where typical thickness values are ~8000 or 9000Å. Also, because of the beam’s grazing incidence, the effective spot size on the wafer can be as large as a few millimeters, making it unusable for direct measurement of gate thickness on product wafers.

X-ray fluorescence (XRF) can measure thickness, but it cannot be readily extended to in-line monitoring of HKMG stacks for some of the reasons discussed below. Even μ-XRF techniques, with spot sizes of 30μm (based on full width at half maximum, i.e., FWHM), are still not small enough to measure on 40μm x 40μm or smaller measurement sites because the effective beam spot, the area that X-ray beam actually covers on films, is about two times bigger. Additionally, measurements with enough precision for gauge capability require data acquisition times that are too long for use in in-line production monitoring. XRF also has limited sensitivity for aluminum and other lighter elements with the atomic number less than that of Si because of the limitations of the Be window of the Si(Li) detector. This, coupled with the uncertainty of placing the X-ray beam at same position on each measurement site adds more to the challenges of measuring such small and non-uniform patterned structures. A laser-interferometer based in situ rate monitor (ISRM), for Al CMP endpoint detection, is often integrated in the CMP system, but it usually does not have enough accuracy and resolution for process monitoring.

Resistivity-based measurements of film thickness also face challenges on very thin films in the HKMG stack, such as the work function metals, which may be 100Å or less. The thickness of the film itself begins to influence the bulk electrical conductivity of the material, and boundary scattering occurs as electrons that would normally bounce off atoms in the film go through to the cladding layers. At this point, the simple relationship between film thickness to series resistance and bulk resistivity breaks down.

For aluminum, 300Å is the lower limit, and for Ti, 200Å. In contrast to TEM, XRR, XRF, and resistivity measurement, the picosecond ultrasonic [4] technique offers an ideal inline on product measurement metrology for monitoring both aluminum and work function (WF) metals. A 0.1ps laser pulse (pump) is focused to about 5×7μm2 spot onto a wafer surface to create a sharp acoustic wave. The acoustic wave then travels away from the surface through the film at the speed of sound. At an interface between materials, a portion of the acoustic wave is reflected back toward the surface while the rest is transmitted. When the reflected acoustic wave reaches the wafer surface, it is detected by another focused laser pulse (probe) which was diverted from the pump pulse by a beam splitter and delayed by a servo controlled variable delay optical circuit. The non-contact, non-destructive nature of this technology enables thickness measurements from tens of Angstroms to 8 microns directly on product wafers. The small spot size (5μm × 7μm2) allows for measurements at site sizes of 30μm x 30μm. Measurements are based on first principles and do not require daily calibrations or reference wafers. In addition to thickness measurements, other parameters such as roughness, density, phase and modulus can be determined to provide additional information about the process.

Pulse measurements in the HKMG process flow

Picosecond ultrasonic measurements are used as checkpoints during various stages of development, integration, and manufacturing of high-k/metal gates. Results from pre- and post-CMP characterization, as well as process tool qualification for work function materials, are discussed.

Pre-CMP characterization and process optimization. Four blanket wafers, two pre-CMP (4000Å and 8000Å) and two post-CMP (polished to baselines [BSLs] BSL+60s from 8000Å as deposited, respectively) wafers were prepared, and picosecond measurements were used to characterize the as-deposited and post-CMP aluminum metal gate in order to fine-tune the Al growth process. Because of the small measurement spot size, measurements can be made to within 1mm edge exclusion to provide information on the edge profiles.

|

|

Figure 1. Line scan across the wafer showing the aluminum thickness profile from -149 to 149mm (top left) and roughness profile (top right),high resolution thickness (lower left) and roughness(lower right) edge profiles from -149 to -141mm.

|

Rapid measurements (2-3s per site) make it possible to acquire 49-point within-wafer uniformity maps as well as high resolution line and edge scans to characterize plating profiles. Across-wafer line scans (Fig. 1) from -149mm to 149mm were made to characterize the Al thickness and roughness variation across the wafer. Because of the small measurement spot size, very high resolution edge scans were also made on all the wafers. Figure 2 shows very symmetric profiles of aluminum thickness~target +1.2kÅ at 1mm exclusion decreasing to target-2kÅ closer to 5mm exclusion, and the very constant roughness (target+/-25Å) even at the wafer edges.

|

|

|

Figure 2. Cross-section TEM graphs of the four aluminum films: a) Pre-CMP 8K, b) CMP BSL, c) Pre-CMP 4K and d) CMP BSL+60s. Correlation between picosecond ultrasonic measurements and TEM on pre- CMP and post-CMP wafers is excellent (R2=0.99).

|

During process optimization, roughness measurements are also used as a qualitative gauge to indicate the presence of pinhole defects. Roughness measurements showed excellent correlation (R2=0.99) to RMS roughness measured using AFM. Accuracy of the PULSE measurements was verified by performing cross-sectional TEM analysis (Fig. 2).

Figure 2 shows the very good correlation between the measurements and cross-sectional TEM thickness. The excellent correlation validates picosecond ultrasonic capability for pre-CMP and post-CMP Al film measurements. Repeatability measurements, both static and dynamic (load/unload) have been tested. The 1σ standard deviation for static and dynamic repeatability is ~ 0.1% and 0.2%, respectively. Long term stability performance on the pre-CMP wafer showed a 1σ standard deviation of ~ 0.01%, confirming that the technique is sufficiently stable and reliable for production monitoring. With information provided from picosecond ultrasonics, process parameters can be optimized and measurements can be made directly on product wafers, eliminating the need for monitor wafers.

Characterization of work function metals. PULSE measurements on the work function and barrier metals were tested. 1σ standard deviation for both static and dynamic repeats is ~ 0.3% or less. Figure 3 shows a cross-section TEM micrograph of a 60Å TiN stack and a 49-point line scan profiles across different barrier wafers. All the films showed profiles consistent with the process. The technology has been successfully and routinely used for similar metal film applications in both the FEOL and BEOL applications. The current performance on the work function metals is consistent with the capability of the technique.

|

|

Figure 3. Cross-section TEM micrograph of TiN barrier metal and 49-point line scans across the wafer for various barrier metal layers used in the HKMG structure

|

Post-CMP characterization on array structures. The critical requirement for production monitoring of the HKMG process is the ability to measure in small test structures, ~ 30μmx30μm, to determine the gate height and uniformity. Post-CMP measurements of the gate stack were made on various sub-micron array structures in ~30μmx30μm sites. Various array structures were investigated for both N-well and P-well stacks of varying array widths with a density of 75%. In this study, results from measurements on 30μmx30μm test features with 5 micron pad arrays were used to demonstrate the capability of picosecond ultrasonic technology.

|

|

Figure 4. A best-fit model to picosecond ultrasonic measurement on 5µm pad array after CMP. The thickness for Al gate height as well as the total thickness of barrier and work function materials can be determined from this signal.

|

Figure 4 shows a picosecond ultrasonic measurement and the best fit model on a 5μm pad array after CMP. Using picosecond ultrasonic technology, thickness for aluminum gate height and combined barrier and work function thickness can be measured simultaneously. Cross-sectional measurements verified the accuracy of these results for a wide thickness range.

Conclusion

Picosecond ultrasonic technology can be used during various stages of process development, integration, and volume manufacturing for monitoring the HKMG stack. Information can be used to characterize the process, and optimize deposition and CMP processes. The accuracy of the technique for monitoring advanced HKMG gate stacks has been confirmed by TEM measurements. The small spot, non-destructive nature of this technology allows for measurements in 30μmx30μm sites directly on product wafers at production-worthy throughputs. The technology offers a complete and ideal metrology tool for non-destructive, non-contact, direct measurement on both blanket and product wafers. Its capability has been extensively proven for both pre-CMP and post-CMP for aluminum processes. The ability to characterize work function barrier layers provides an additional benefit for the use of the technology for HKMG process monitoring.

Acknowledgments

S.F. Huang, Y. R. Yang, C. L. Yang , and J. Y. Wu of 1-United Microelectronics Corp. are co-authors. PULSE is a trademark of Rudolph Technologies.

References

- M. Bohr, R. Chau, T. Ghani, K. Mistry, IEEE Spectrum, Oct. (2007) pp. 30-35.

- V. Misra, G. Lucovsky, G. Parsons, MRS Bulletin, vol 27, no3, (2001) pp. 212-216.

- R.Chau, J. Brask, S. Datta, G. Dewey, M. Doczy, B. Doyle, et al., Microelectronic Engineering, vol 80, June (2005) pp. 1-6.

- C. Thomsen, H. T. Grahn, H. J. Maris, J. Tauc, Phys. Rev B, vol 34, no 6, (1986) pp. 4129-4138.

- M. Hsieh, J. Yeh, M. Tasi, K. Wang, J. Tan, S. Leary, Proc. SPIE, Vol. 6152, 61522C, March (2006) pp. 815-828.

Biographies

Johnny Dai received his PhD at Fudan U., Shanghai and is a principal applications scientist at Rudolph Technologies, One Rudolph Road, P.O. Box 1000, Flanders, NJ 07836 USA; ph: 973-448-4479; email [email protected].

Solid State Technology | Volume 54 | Issue 3 | March 2011

More Solid State Technology Current Issue Articles

More Solid State Technology Archives Issue Articles

Listen to Trafas’ interview: Download (iPod/iPhone users) or Play Now

"This application is targeted to customers who want to beat the lithography roadmaps for overlay and registration, in conjunction with

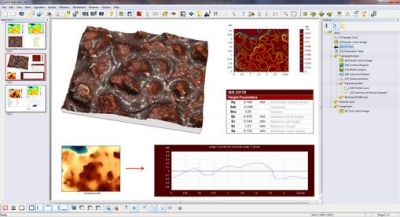

"This application is targeted to customers who want to beat the lithography roadmaps for overlay and registration, in conjunction with  Entry-level Leica Map Start software is used in conjunction with LAS Montage. LAS Montage acquires a series of image planes at known spacing covering the in-focus region of a specimen with a Leica microscope. From this stack a depth map and an extended focus image are derived and analyzed by Leica Map. In Leica Map Start, surface topography can be viewed at any zoom level and any angle in real time. Color and intensity image overlays facilitate the location of surface features, including defects. Distances, angles, and step heights can be measured. Height and functional parameters are calculated in accordance with the latest ISO 25178 standard on areal surface texture. Optional modules can extend the capability to surface texture and contour analysis.

Entry-level Leica Map Start software is used in conjunction with LAS Montage. LAS Montage acquires a series of image planes at known spacing covering the in-focus region of a specimen with a Leica microscope. From this stack a depth map and an extended focus image are derived and analyzed by Leica Map. In Leica Map Start, surface topography can be viewed at any zoom level and any angle in real time. Color and intensity image overlays facilitate the location of surface features, including defects. Distances, angles, and step heights can be measured. Height and functional parameters are calculated in accordance with the latest ISO 25178 standard on areal surface texture. Optional modules can extend the capability to surface texture and contour analysis.