by James Montgomery, news editor

March 25, 2011 – Applied Materials had its Analyst Day on March 23. Key takeaways included: Where wafer-fab equipment demand is strongest, how solar manufacturing technology can expand, and why tablet computers and electric vehicles are underpinning a resurgence in 200mm demand.

Quickly updating on the Japan earthquake & tsunami situation, AMAT chairman/CEO Mike Splinter noted that the company’s 650 staff and families are all safe; some of the company’s 22 facilities in Japan sustained minor damage but all are back in operation, he noted. There has been "minor impact" on customers, but so far there has been "no material impact" on AMAT through 2Q11 — though the situation is still "dynamic and unpredictable," he added. Joe Flanagan, SVP of operations, added that the company has been able to address risks for all its Tier 1 and Tier 2 suppliers, and in some places concluded mitigation plans. There’s some infrastructure questions, but "we’re making prudent assumptions" and planning around them, he said.

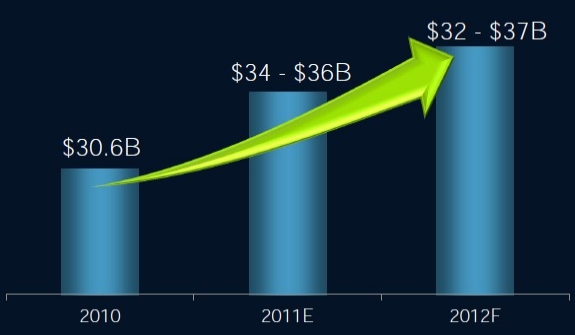

Growth in SSG/semiconductors. AMAT EVP Rhandir Thakur offered updates on the semiconductor sector as a whole and the company’s own numbers:

- Revenue growth of 170% — outpacing the overall WFE sector, thanks to gains in 2009/2010. Operating profit model targets $1.9B (Semitool is turning accretive ahead of plan). 2011 priorities for SSG: launch >12 new products, gain >1% share in 300mm WFE, >$2B profit.

- AMAT still expects 18 new fabs/expansions in the next 2-3 years, translating to 1.2M more wafer starts/month, and $70B-$80B in WFE spending.

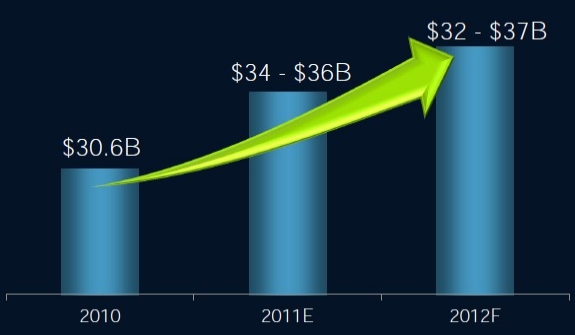

|

| (Source: Gartner, Applied Materials) |

The company reiterated its areas of share gain since 2008: six points each in PVD and transistor fabrication, seven in CMP, and two in CVD. Translation: $1.5B growth in revenues. Looking forward AMAT expects four points in etch (foundries and memory), and some inspection; in plating/ECP the addition of Semitool has helped with business in both interconnect and wafer-level packaging.

Thakur noted that moving from the 65nm to 2Xnm node, memory and foundry/logic makers will be adding over 150 process steps. And more than 70% wafer starts in 2012 will be on advanced nodes (≤45nm process technologies), and that’s where 80% of spending goes. Added complexity — including 3D chip technologies, transition to HKMG, and EUV lithography (especially if it’s delayed) — is good news for AMAT, he summed.

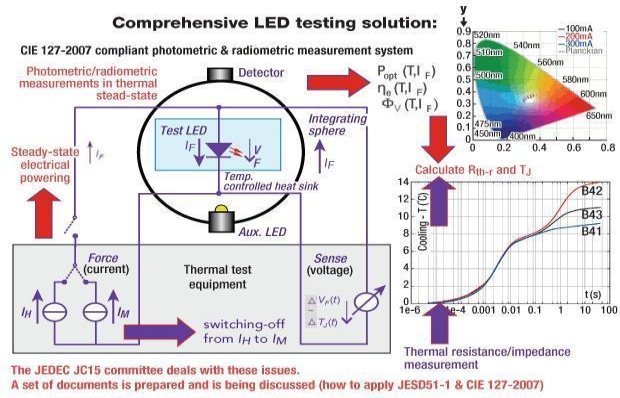

Solar steady, LEDs coming up. EVP Mark Pinto pointed to HB-LED, new products for c-Si PV and "product enhancements" for thin-film PV. New growth is seen in extending Baccini Esatto technology in front metal, point contact, and selective emitter, enabling "up to a 2 point efficiency gain," though this discussion was "short on some of the technical details," writes Barclays analyst CJ Muse in a report. After three years with negative-teens operating margins, Pinto projected 26% operating margins (non-GAAP) in 1Q11, and gaining more than five points of share in wafering systems, Pinto pointed out.

In the future AMAT is looking at Gen3 c-Si and "disruptive" thin-film technologies, as well as expanding into manufacturing equipment for energy storage/batteries.

Still, there’s increasing concern about possible solar overcapacity and a slowdown in capacity additions. "At current run rate, Solar is roughly 20% of the revenues and slowdown in the area can be significant," writes Credit Suisse analyst Satya Kumar, in his own research report.

AMAT did not release its anticipated MOCVD tool for LED manufacturing, though it claims to have received signoff and actual sales from it. "It would appear that there was a miscalculation made in terms of not targeting China as an early adopter but rather as a fast follower," notes Barclays’ Muse. More pessimistically, Credit Suisse’s Kumar is "skeptical" of any traction from an AMAT LED-MOCVD product, "given that the competition is well established and the product is much behind original schedules."

In the display segment, sales are seen growing to $1B, driven by expansions into OLED and touch screens (i.e. areas requiring higher capital intensity), capacity expansion in China (more and larger TVs), share gains with its Pivot PVD tool. For touch screen manufacturing, the company is pushing a new Aristo PVD tool and sees opportunities in CVD for low-temp polysilicon. AMAT also sees a play in scaling OLED capacity and flexible displays (i.e. inkjet printing).

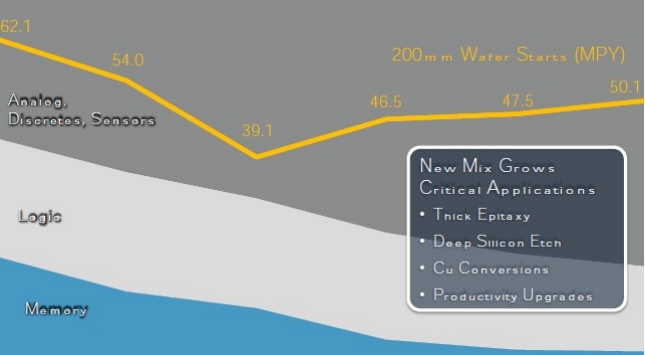

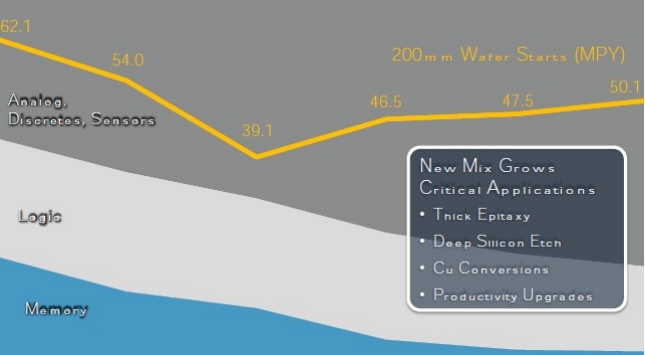

Tablets, EV driving the 200mm resurgence. An update from AMAT’s services arm (AGS) reiterated that demand for legacy 200mm equipment continues to be stronger than expected — and will remain so into 2012. The company has reopened its 200mm line in Austin that it took offline in 2009, and is retooling its entire supply chain to refresh for 200mm spares/service — many suppliers had discontinued their 200mm components or were simply no longer in business.

What’s behind this 200mm resurgence? While memory is almost completely converted to more economical 300mm, and CMOS logic has mostly gone over as well, what’s more than made up for that are analog devices and discretes and MEMS devices, for products in automotive, consumer — and especially tablet computers, according to group VP/GM Charlie Pappas. Apparently the iPad is heavily reliant upon 200mm silicon (75% of its silicon), which has lit a fire under process areas such as thick epitaxy, deep silicon etch, copper conversion, and productivity upgrades, he noted. Another driver: hybrid vehicles, which require a lot of power management. (His quick math: each EV car needs the equivalent of one 200mm wafer…and some estimates forecast 20M such vehicles in China in a couple of years, pushing wafer output back to prior peaks.) AMAT says it will take several quarters to fully catch up with the 200mm backlog built up in late 2010 (75% worked through by fiscal 3Q11, and fully caught up by F4Q11, i.e. Oct. 2011).

|

200mm recovery and retooling creates opportunity. MPY = millions/year.

(Source: iSuppli, Applied Materials) |