by John Ellis, SEMI

February 12, 2010 – For the lifetime of the semiconductor industry, reduced cost and increased functionality have driven end applications and sales. The main lever in achieving both of these has been through the ever-advancing reduction in feature size achieved through the inventiveness and hard work of the engineers and scientists in the industry, government, and universities. Increased functionality through enhanced chip and system design and ingenious software add to the remarkable improvement in electronic systems capability. All of this growth has been built on the performance of the chips themselves. It is no surprise that manufacturers continue to strive for the next improvement, as it is the lifeblood of the entire supply chain.

The changing nature of the industry has presented manufacturers with new realities. The semiconductor industry went through an extended time of incredible growth up until the dot-com bubble. However, growth has slowed considerably as the industry has matured and saturated numerous market segments. The slow growth has led to a significant reduction in the number of fabs required to meet market demand and a smaller market for the suppliers of capital equipment, which ultimately limits the overall amount of R&D resources the supplier community has available for continued improvements.

A SEMI white paper ("Semiconductor Equipment and Materials: Funding the Future") published in October 2005 outlined this looming problem, predicting that by 2010 the industry would need $10.4B to fund basic technology R&D. The industry bust of 2008-2009 has made the situation worse — only $2.1B of the $10.4B needed for R&D will be available as we look forward to 2010. With these constraints the industry has to make hard choices about what will and won’t be funded. Unfortunately, the industry doesn’t operate as one entity, as there are many forces, interests, and objectives at hand, and not all can be satisfied. So, companies have to make very smart choices in their investment choices.

New markets have opened up for many semiconductor suppliers, including photovoltaics, the "Smart Grid", high-brightness LEDs, NEMS/MEMS, and flexible and printed electronics and displays. While all are related to semiconductors, each market requires its own investment in market research, needs assessments, and focused R&D that can further complicate a company’s strategy.

SEMI’s role is to look objectively at the overall market conditions, economic factors, and timing to provide our members with data to make optimal strategic and investment decisions for their own companies. In this vein, we would like to present our perception of the current status of the economics and timing of a 450mm wafer transition.

Economics

There continues to be a pervasive misconception that a wafer-size transition alone can provide a significant cost saving for the industry. Expectations of 30% cost savings have been repeated so often that it may seem that it is a fundamental law of wafer-size transitions. As was pointed out in SEMI’s Equipment Productivity Work Group’s (EPWG) paper on the Economics of 450mm, this expectation has not been based on objective analysis. The following data, based on analysis from our member companies, raise large questions which have been overlooked by IC Knowledge in their assessment. For example, Scotten Jones states that at IC Knowledge:

"We have assumed 450mm equipment will have similar throughput to 300mm and cost 1.3× as much."

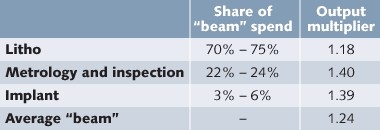

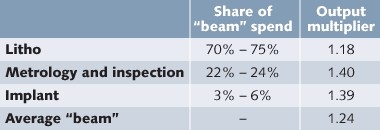

This assumption has not been substantiated by objective analysis. The reality is that beam tools — tools whose throughput is a function of the area they can scan in an hour — can only have their speed increased within certain limitations due to basic physics. (The details of our analysis are available in our EPWG report.) The key is that IC Knowledge assumes the same number of wafers per hour processed, providing the increased area per hour improvement in speed. Beam tools can handle fewer wafers per hour for an equivalent equipment wafer scale up. Whereas IC Knowledge’s multiplier on throughput would be 2.31× (2.25× increased area plus additional gains at the edge), a beam tool’s output multiplier is an average of 1.24×, or almost 50% less (Figure 1). This analysis has been acknowledged by industry groups working with SEMI. IC Knowledge’s assumptions on consumables cost and wafer costs are also not supported by analysis.

All of the optimistic predictions of cost savings accrued by going to 450mm wafers assume that 450mm wafers will cost approximately the same per unit area as do 300mm wafers. However, there are many technical challenges that must be faced by wafer manufacturers to develop the extremely high quality substrates that will be required that will make this assumption hard to achieve. SUMCO offers a detailed analysis of their investigation. Readers are encouraged to download the EPWG analysis which provides details on our analysis.

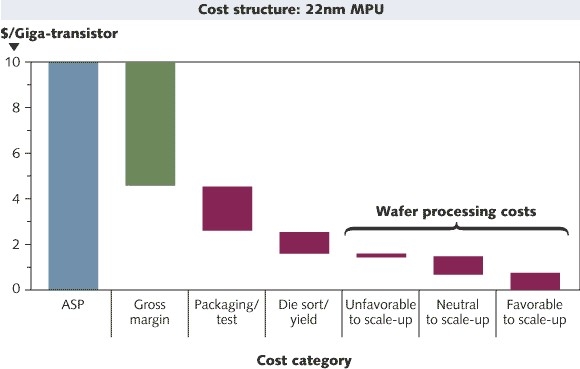

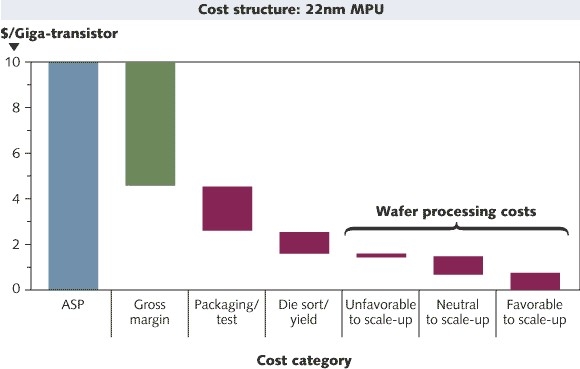

It is important to recognize the overall impact on the industry that a transition to 450mm might have, over and above any potential cost savings in wafer processing. Figure 2 below shows a chart that details the expected cost structure for a 22nm microprocessor. The data are based on IC Knowledge reports. Note that the wafer processing costs make up about 15% of the overall price (to the customer or ASP) of the final product. Even if a reduction of 30% in overall costs were obtained, this would result in a net savings of 5% of the overall part cost, and consumers might see half of this. Our study shows that perhaps 8% of the overall costs would be reduced by a scale-up. This leads to the obvious question — is a projected $25B investment in equipment R&D justified for 8% improvement?

IC Knowledge has stated that 300mm Prime will not meet its productivity improvement objectives. It is a substantial jump to say that 450mm, therefore, is necessary. To conclude that 300mm Prime effort has failed would be misleading. It is our view that the distraction caused by focus on 450mm, along with the massive downturn experienced in 2008-2009, has diluted any serious, concerted efforts toward re-architecting 300mm fabs. We prefer to say that 300mm Prime, or its successor, 300mm Next Generation Factory, has not yet been given a chance.

Timing

Originally, the industry had targeted the transition to 450mm for the 32nm node, but this has now slipped to the 22nm node for production. At the Industry Strategy Symposium held by SEMI in January, 2010, some analysts, e.g. Bob Johnson from Gartner, were predicting that the transition would most likely be 11nm, if it happens at all. This is more consistent with the announcement of 22nm processors occurring in 2011 by Paul Otellini, CEO of Intel. It is also consistent with supplier statements that they cannot afford to develop process technology on two platforms at the same time — the cost is prohibitive and the overall market not big enough to justify the investment. However, ISMI has announced its continued plans for a demonstration program at 32nm and pilot lines at 22nm.

11nm on 450mm wafers?

There are potential benefits in setting 11nm as a target for 450mm introduction. This delay may provide time to wring out the serious technology issues equipment manufacturers must resolve in the non trivial scale-up to 450mm. Recent presentations at the 450mm Workshop at SEMICON Europe 2009, organized by Fraunhofer Institute, show that for most tools there are unforeseen technical impacts that have to be analyzed and dealt with. Funding for research on these difficult areas is strongly encouraged, and SEMI applauds the European Commission for providing a program to help suppliers in these efforts.

However, there are a lot of technology challenges to be overcome at 16nm unrelated to the transition to 450mm. These include: double patterning, EUV lithography, new materials, and complex levels of process integration beyond the capabilities of most equipment suppliers. Knowing that our big lever is feature size reduction, and that there may not be enough R&D funding to do everything, the question is what would we give up, as an industry, if we had to?

What happens at 11nm? There have been implications that new materials, perhaps even a new substrate, will be required. In an extreme case, but unlikely case, we might see that 450mm is a one-node solution.

Funding

Now to the hard part that not even SEMI has fully analyzed. Several analysts have estimated the R&D investment required for suppliers at $25B to $30B (VLSI Research and IC Knowledge). SEMI’s investigations support this number. However, no one has looked at how this effort will be funded. In the 300mm transition, it is generally agreed that suppliers funded the bulk of the R&D required for equipment. It is a more controversial issue to determine whether the suppliers have ever recouped their costs. Forgoing this discussion, we’ll jump into a simple, high-level analysis on whether the supplier community is equipped to fund the R&D needed for 450mm.

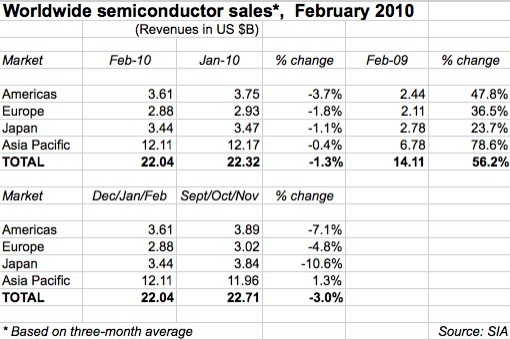

In our R&D Funding the Future white paper, SEMI found that suppliers have been able to spend about 14 to 15% of their overall revenue on R&D activities. Recent analysis by SEMI continues to substantiate this amount. Of this total, about 10% is spent on research. The balance of the funding goes toward many activities, including equipment support and continuous improvement. Of course, this funding goes toward all R&D — including technology, e-manufacturing, new business (PV), etc. SEMI’s current estimate for revenue for the equipment industry for 2009 is approximately $14.1B, growing by over 47% in 2010 to $20.74B. If the full 15% of the supplier R&D budget for 2010 was applied toward 450mm, there would be $3.11B available for a 22nm node transition, with slightly more available for a 16nm node transition. Most of this funding is already committed toward funding technology advancements, including process technology, 3D TSV technology, and materials. This amount falls far short of the estimated $25B required for 450mm.

Even if there were substantial cost-savings by moving toward 450mm wafers, the timing and funding issues are serious concerns. A transition to 450mm will be a very difficult undertaking and will require a coordinated effort across the entire supply chain. Only three chipmakers (those with serious capital equipment budgets) have announced support for 450mm, so a coordinated effort seems difficult at this point. Industry Readiness

It is not SEMI’s role to encourage or discourage a particular industry decision. That is ultimately left up to the market. In fact, the SEMI Standards program is actively pursuing development of standards that are 450mm wafer-size specific. If the industry is going to be ready for a transition at some point in the future, these standards are absolutely necessary in order to reduce overall development costs.

Since the supplier industry clearly does not have sufficient funding to tackle the issues surrounding 450mm and keep other technologies on-track, we are supportive of government funding to look into key research issues. We are particularly supportive of funding that can be channeled toward ‘dual-use’ technology improvements that may benefit 300mm now while being applicable toward 450mm later.

A true collaboration from industry, where key stakeholders have contributed substantial funding toward supplier R&D efforts, would be a key sign that the proponents of 450mm are very serious about moving it forward with some "skin in the game". We have not seen this in any significant way.

In the meantime, SEMI will continue to work with industry in evaluating the economic, technology, timing, and funding issues so that our members have as a large set of data upon which to base individual company strategic decisions.

Biography

John Ellis is VP of standards and technology at SEMI.