December 4, 2009 – After shrinking by nearly two-thirds over the past two years to lowest levels in more than two decades, global semiconductor equipment sales will surge mightily in 2010 and continue solid growth into 2011, according to updated forecast information from SEMI.

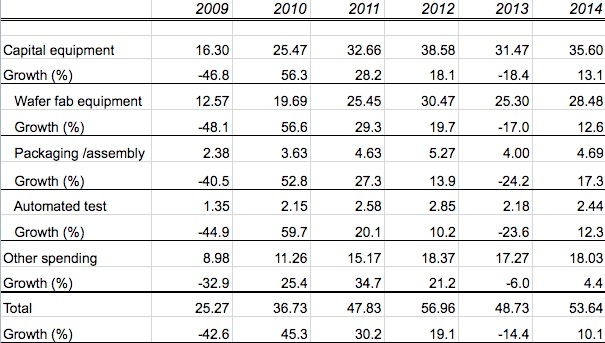

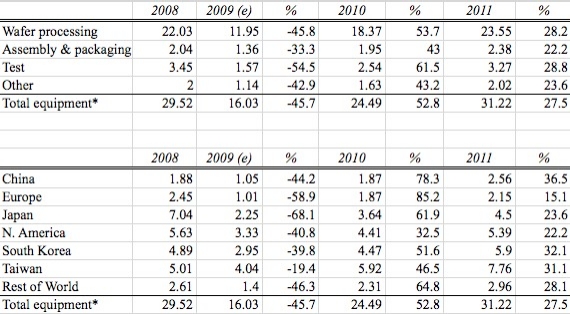

The new forecast pegs the final bloodbath of 2009: a -46% decline in total chip sales (33%-55% across individual segments) to $16.03B, the largest single-year decline since SEMI started tracking the numbers in 1991. That’s on top of a -31% decline suffered in 2008, to $29.52B.

But SEMI also projects an intense pickup in chip tool investments on the horizon: a 53% increase in 2010, and as much as 61% for backend application, driven by improved spending across memory (notably NAND flash), foundries, and packaging subcons, SEMI notes.

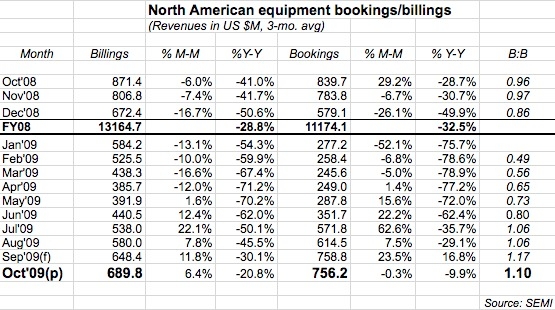

|

| Forecasts by equipment segment and region, in US $B. *Totals and percentages may differ due to rounding of numbers. (Source: SEMI) |

By equipment segment, test equipment has taken the brunt of the 2009 downturn (-54%, to $1.57B), but will reap the most benefits in both 2010 (61%, to $2.54B) and 2011 (29%, to $3.27B). Assembly/packaging equipment is on the other end of the scale, suffering "only" a -33% decline in 2009 (to $1.36B), will keep to the curve in 2010 (43%, to $1.95B), and keep growing in 2011 but slightly less than other segments (22%, to $2.38B).

By region, 2009 was especially harsh to Japan (-68%) and Europe (-59%), but they will lead the march in 2010 with eye-popping growth (62% and 85%, respectively), alongside China (78%) and Rest-of-World (65%). China, ROW, and South Korea will lead in growth in 2011, each with >36% increases Y/Y.

Overall fab spending is expected to spike even more in 2010 (65%) — but with no new fabs are planned for the coming year, that raises the question about the industry’s preparedness to actually meet future demand, warns Christian Gregor Dieseldorff, with SEMI Industry Research and Statistics.

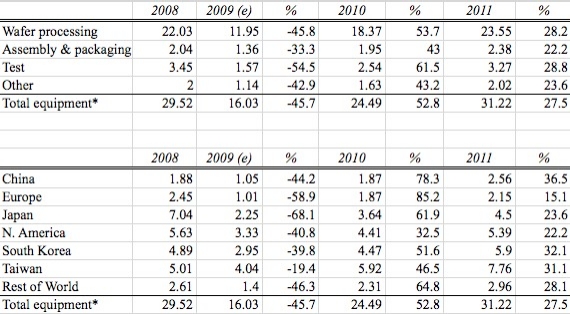

|

|

| Money spent on frontend facilities (R&D, pilot, volume fabs), in US $B. (Source: SEMI World Fab Forecast) |

"Most companies will not invest in new facilities or significantly in new capacity in 2010," instead preferring to invest in technology upgrades, he writes in a new report. TSMC, Samsung, GlobalFoundries, and others are all in line to greatly increase spending, he notes. Construction spending is expected to surge 70% to $2.7B for an estimated 23 projects — but none of those are new facilities. A year ago SEMI’s World Fab Forecast projected 19 new fabs would start or resume in 2010; now, post-downturn, no additional plans are finalized, though five of those 19 are shells where delayed activity are expected to resume. In fact, 49 facilities have or will close by the end of 2010, which will reduce installed capacity by 4%-5%, a decline "unprecedented over the last 20 years" — even the post-2001 slump didn’t suffer a Y/Y decline, Dieseldorff notes.

In 2010, installed capacity is expected to put back 4%-5% installed capacity — but that means only returning to 2008 levels of demand. With utilization rates projected in the 80%-95% range (according to recent SICAS numbers), capacity sell-outs become a likelihood. Industry watchers now predicting anywhere from 10% to 22% semiconductor revenue growth in 2010. And with fabs investing in technology upgrades, not capacity, "the future growth rate of installed capacity appears not in sync with demand," he writes. It takes a year or more from groundbreaking to production ramp, so either capacity will be limited through 2010, or some devicemakers will realize they’ll be caught short and quickly start fab plans for extra capacity in 2011. And, he notes, "the one who is first, benefits the most."