|

Executive Overview Two complementary techniques that provide in-line metrology solutions for epitaxial layers, such as SiGe or Si:C on Si wafers are presented. These techniques are high-resolution X-ray diffraction (HRXRD) and X-ray reflectometry (XRR). The capabilities and principles of both techniques will be summarized and representative data will be used to demonstrate both the principles and utility of combined HRXRD and XRR for the metrology of strained epitaxial layers. Both techniques are non-destructive and provide calibration-free, first principles measurement capabilities. |

Paul Ryan, Matthew Wormington, Alexander Tokar, Jordan Valley Semiconductors, Durham, UK

Strain engineering is an accepted and important method to enhance the performance of advanced complementary metal oxide semiconductor (CMOS) devices. Process-induced local strain, is currently the mainstream technology used to increase the hole mobility in advanced pMOS transistors. Here, recesses are etched in the source and drain regions and SiGe is selectively deposited in the recesses to introduce uniaxial compressive strain in the channel. Electron mobility improvements in nMOS transistors have, to date, been largely achieved through the use of stress liners, but this technology becomes less effective with continued scaling. As such, selective epitaxial growth of Si:C in the source/drain is being developed as a method for introducing compressive strain into the channel for potential adoption at the 22nm node and beyond. As strain engineering is further adopted and refined by semiconductor manufacturers there is a need for improvements in the control of these processes.

In this article we will present two complimentary techniques that provide in-line metrology solutions for epitaxial layers, such as SiGe or Si:C on Si wafers. High-resolution X-ray diffraction (HRXRD) and X-ray reflectometry (XRR) can offer both accurate and precise measurements of thickness, composition, density and relaxation [1]. We will summarize the capabilities and principles of both techniques and describe a tool (JVX 7200) that has been developed for in-line measurements on product wafers. We will compare and contrast the new measurement approach with more traditional X-ray tools and discuss its advantages in terms of spot-size, throughput and reliability. We will present recent developments that allow XRR to be made on metrology pads within a scribe line. Representative data will be used to demonstrate both the principles and utility of combined HRXRD and XRR for the metrology of strained epitaxial layers.

High-resolution X-ray diffraction

HRXRD has been utilized for many years for the characterization and metrology of epitaxal thin films in both the compound and silicon semiconductor industries. Traditionally, the HRXRD technique has required a highly parallel X-ray beam (to ~10 arcseconds divergence) incident on the sample. The intensity of the diffracted X-rays is measured as a function of angle with respect to the sample surface, in a step-wise manner using a high-precision goniometer. By determining the incident and exit angles of the X-ray beam at intensity maxima in the spectrum, the strain, and hence lattice parameters, of the individual layers with respect to those of the substrate can be determined. These structural parameters can be converted to composition and relaxation of the layer in question using well known material relations. Thickness information of fully strained layers can also be determined from interference fringes that are present in the diffracted intensity from such samples.

A key disadvantage of the traditional HRXRD technique, especially on small metrology pads, is the low throughput. The comparable low intensity of an X-ray source compared to optical techniques, and the scanning nature of the technique lead to measurement times per point of several minutes. The in-line use of the technique in the silicon semiconductor industry has described [2] but has been typically limited to R&D and providing chamber qualification for the epitaxial reactors. One, or perhaps two, measurements were typically done using daily monitor wafers to check both the reactors and provide a baseline fast optical method, such as spectroscopic ellipsometery (SE), used for process monitoring of the product wafers. This approach was adopted largely due to necessity rather than being an optimal solution and such an approach is not without its problems. For example, correlations exist between composition and thickness measurement of SiGe layers using SE. The problems become much more acute at, and beyond, the 40nm node due to the use of multiple layer stacks and potential introduction of Si:C at 22nm, which typically only has a C concentration of ~1-2% compared with ~10-20% for Ge. This low composition essentially renders the Si:C layer invisible to optical techniques.

|

Figure 1. The Fast HRXRD method, using a convergent beam and 1D detector. |

To help overcome these shortfalls with current epi layer metrology, we have developed a method for HRXRD that addresses the main issues hampering its use as an in-line metrology of high-quality epilayers on product wafers, i.e., low-throughput, and hence sampling, and spot size. The new method (Fig. 1) uses a focused, monochromatic X-ray beam incident on the wafer, with a one-dimensional detector. This enables all incident angles to be illuminated and the entire diffracted intensity to be acquired simultaneously. This approach allows HRXRD data from product wafers to be measured in tens of seconds rather than tens of minutes. This new FastHRXRD typically provides an order of magnitude speed improvement over conventional scanning measurements.

|

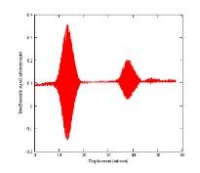

Figure 2. Comparison of FastHRXRD measurements of fully strained (green curve) and partially relaxed (blue curve) on a product wafer. Typical acquisition times for composition and thickness determination are ~100s. |

Figure 2 shows two spectra collected on the new fast HRXRD system. Both spectra were collected in ~ 100 seconds from patterned wafers. The green curve shows data from a fully strained SiGe bilayer, with a clear SiGe peak on the left of the spectrum, from which composition is determined, and higher frequency fringes either side of this peak, from which the SiGe thickness can be determined. The blue curve shows a similar spectrum from a wafer where the Ge fraction was slightly too high and resulted in a partially relaxed test pad: the broad peak position gives information on the composition of the layer but, due to the relaxation present within the layer, no thickness fringes are seen. Therefore, the thickness cannot be determined from the HRXRD and an alternative method must be found.

X-Ray Reflectivity

X-ray reflectivity (XRR) is used for the measurement of thin, multilayer properties such as thickness, density, and roughness. XRR measurements are highly sensitive to the electron density of sub-micron structures irrespective of their crystalline nature. Consider an X-ray beam illuminating the surface of a sample at low (1-2°) incidence angle. The index of refraction for all materials in the hard X-ray wavelength region is slightly less than one, consequently, the X-ray beam is totally reflected if the incidence angle is a smaller than a certain critical angle. In this region, the penetration depth is only a few nanometers. At slightly higher angles, the X-rays start to penetrate and are reflected from the interfaces of thin-films resulting is a series of interference fringes. In the Jordan Valley system, a convergent beam illuminates all of these incident angles simultaneously, and a one-dimnsional detector enables parallel acquisition of the entire reflected intensity distribution in the detector of the XRR spectrum. This allows for extremely high throughput XRR, compared to more traditional scanning methods. Speed improvements of one to two orders of magnitude are typical with blanket wafer measurements taking only a few seconds per site.

Another limitation of XRR systems, to date, has been the length of the X-ray spot on the sample due to the glancing angle geometry. In the past, the smallest spot-size that was achievable was several millimeters. With the recent development of our latest generation of FastXRR (called VEGA), sub-mm spot sizes can be achieved and true scribe line measurements are possible. This has been done by improved control of the knife position allowing height above the wafer surface to be maintained at only a few microns.

|

Figure 3. Measured XRR data (blue curve) and best-fit simulation (red curve) from a 600µm test region (two adjacent 300μm SIMS pads) using the Vega FastXRR channel. Typical acquisition times for scribeline measurements is a few tens of seconds. |

Figure 3 demonstrates the XRR data from two adjacent 300μm SIMS pads using the new channel. A clear interference pattern can be seen from the SiGe layer, allowing the thickness to be determined in tens of seconds. Furthermore, since XRR is not sensitive to the crystalline perfection of layers it can also be applied to amorphous and polycrystalline film stacks. This allows the FastXRR channel to also be used for metrology of other important front-end film stacks, such as those in high-k/metal gate processes or amorphous carbon hardmasks encountered for double-patterning and deep trench lithography applications where conventional optical metrology can struggle.

Combining HRXRD and XRR

The combination of the new HRXRD and XRR channels allows for the fast and accurate determination of all the critical SiGe parameters: thickness, composition and relaxation for process control. The combination can be extended to the determination of the individual layer parameters within SiGe multilayers for process diagnostics or during R&D.

|

Figure 4. High-speed maps of the Ge composition measured by Fast HRXRD (left) and thickness measured by Fast XRR (right) over a 300mm SiGe//Si(001) wafer. |

Figure 4 shows how this combination works in practice for process control, with the composition and thickness of a SiGe layer mapped using the complementary techniques. By utilizing the strengths of each technique, the strain sensitivity of the diffraction and the thickness sensitivity of the reflectivity, unsurpassed accuracy and repeatability of the key SiGe metrics can be achieved to control the process.

Conclusion

The combination of HRXRD and XRR for the analysis and control of critical parameters of epitaxial growth has been presented with example data shown for SiGe layers. Significant improvements to each technique have been described including a new Fast HRXRD channel that improves throughput, as well as a reduction in spot-size for product monitoring of SiGe and Si:C. Additionally, a new channel can now perform XRR on scribe-line metrology pads, and not just blanket wafers, to enable product monitoring of a variety of front-end films. By using these complementary techniques, the JVX 7200 can determine the thickness, composition and relaxation of SiGe and Si:C layers with spot-size and throughputs suitable for in-line use.

References

1. D. K. Bowen, B.K. Tanner, X-ray Metrology in Semiconductor Manufacturing, Taylor & Francis (2006).

2. M. Belyansky, A. Domenicucci, N. Klymko, J. Li , A. Madan, Solid State Technology, 52 (2009)

Biographies

Paul Ryan received BSc(Hons.) and PhD degrees in physics from the U. of Leeds, UK, and is a Corporate VP/UK site manager for Jordan Valley. For more information, contact Alon Kapel at Jordan Valley Semiconductors IL Ltd, Migdal Ha’emek 23100, Israel; ph.: 972-4-6543666 x134, email [email protected].

Matthew Wormington graduated with a BSc(Hons.) in physics from the U. of Birmingham, UK and is the CTO at Jordan Valley Semiconductors.

Alexander Tokar received an engineering degree from Steel and Alloys Institute, Moscow, majoring in X-ray diffraction, and received his PhD from the Israel Institute of Technology (IIT) in materials science. He is a manager, worldwide application support at Jordan Valley Semiconductors.

More Solid State Technology Current Issue Articles

More Solid State Technology Archives Issue Articles

May 24, 2011 — Sunrise Optical LLC debuted the Zebraoptical low coherence fiber optic interferometer with microscope attachment. The Zebraoptical Integrated Metrology Tool (ZIMT) provides metrology readings on

May 24, 2011 — Sunrise Optical LLC debuted the Zebraoptical low coherence fiber optic interferometer with microscope attachment. The Zebraoptical Integrated Metrology Tool (ZIMT) provides metrology readings on

Listen to Hsing’s interview:

Listen to Hsing’s interview:

An addition to KLAC’s Component Inspector series, the CI-T620 is a fully automated optical inspector of

An addition to KLAC’s Component Inspector series, the CI-T620 is a fully automated optical inspector of