May 25, 2011 — imec’s 3D integration industrial affiliation program (IIAP) partnered with Atrenta Inc., SoC realization products provider to semiconductor and electronic systems industries, to developed an advanced planning and partitioning design flow for heterogeneous 3D stacked ICs.

Cost-effective, rapidly ramping 3D ICs require robust, accurate partitioning and early prototyping. The flow imec and Atrenta are working on aims to minimize design iteration rounds. They demonstrated their first EDA tool flow for 3D design at DAC 2010. 3D stacked ICs reduce package footprint, and offer shorter and faster interconnects, possibly at lower costs. Stacked IC designs can be modular, and reused over various systems. The technology best suits mobile and high-performance applications, stacked DRAM, imagers, and solid-state drives.

The number of potential processes to resolve a given system design problem (e.g., front to front, front to back, silicon interposer, technology choice for slices, via configurations, partitioning, etc.) is huge. Creating multiple full design solutions for comparison is prohibitively expensive and time-consuming. Robust, accurate partitioning and prototyping early in the design process, well before detailed implementation begins, will avoid much of this trouble.

Other 3D design challenges include thermal profiles (heat dissipation) and mechanical stresses from assembly configurations. Imec has developed compact thermal and mechanical models for rapid generation of heat dissipation and mechanical stress maps and has validated them using real 3D DRAM-on-logic packaged devices. Atrenta’s SpyGlass Physical 3D prototyping tool creates design "floor plans," which can be combined with the stress models developed by imec, to compare options in different scenarios before full design implementation.

Imec and Atrenta will be demonstrating this flow at the Design Automation Conference (DAC) in San Diego, CA, June 6-8, 2011, in the Atrenta booth (1643). See design partitioning across a 3D stack with routing congestion analysis, through silicon via (TSV) placement and backside redistribution layer (RDL) routing support. The demo will also include a display of thermal profiles on the 3D "floor plan." For more information about Atrenta’s demonstrations at DAC visit: http://www.atrenta.com/DAC2011/sessions_short.html

Imec performs world-leading research in nanoelectronics. Further information on imec can be found at www.imec.be.

Atrenta provides SoC Realization solutions for the semiconductor and electronic systems industries. Learn more at www.atrenta.com

Subscribe to Solid State Technology/Advanced Packaging.

Follow Advanced Packaging on Twitter.com by clicking www.twitter.com/advpackaging. Or join our Facebook group

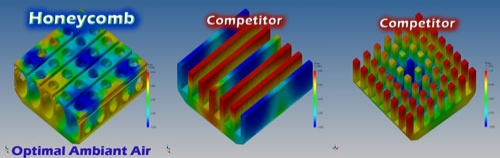

producing a steady flow of cool air inside the heatsink. Honeycomb heatsinks can be used with either plastic or metal/ceramic BGA packages, depending on the thermal interface material (TIM).

producing a steady flow of cool air inside the heatsink. Honeycomb heatsinks can be used with either plastic or metal/ceramic BGA packages, depending on the thermal interface material (TIM).

In an exclusive series of blogs, imec reports from its International Technology Forum (ITF) last week in Brussels. Els Parton, science editor, imec, shares Jy Bhardwaj’s (Philips Lumileds) points about LEDs costs improvements.

In an exclusive series of blogs, imec reports from its International Technology Forum (ITF) last week in Brussels. Els Parton, science editor, imec, shares Jy Bhardwaj’s (Philips Lumileds) points about LEDs costs improvements.  reflects the acquisition of Chip Supply last November by Micross Components in Los Angeles, CA. Micross provides specialist products and services for

reflects the acquisition of Chip Supply last November by Micross Components in Los Angeles, CA. Micross provides specialist products and services for  Construction commenced in Q1 2011 and production operations are expected to begin in Q1 2012. The expansion will bring the total factory size to 56,000 square meters (600,000 square feet), with expanded test capability to match the new production output. Carsem expects to attract new potential customers with the capacity boost.

Construction commenced in Q1 2011 and production operations are expected to begin in Q1 2012. The expansion will bring the total factory size to 56,000 square meters (600,000 square feet), with expanded test capability to match the new production output. Carsem expects to attract new potential customers with the capacity boost.