January 18, 2010 – A quick highlight list of Intel’s blowout 4Q09 numbers, released after markets closed on Thursday 1/14:

– Revenue $10.6B, up 13% Q/Q and 28% Y/Y

– Net income $2.3B (includes $1.25B settlement with AMD), up 23% Q/Q and nearly ninefold from 4Q08

– Gross margin a record 64.7%, up 7 points from 3Q09 and 11.6 points vs. 4Q08. (FY09 margins 55.7% were flat with 2008)

And its outlooks for 1Q10:

– Sales down to $9.3B-$10.1B

– Gross margins slipping to 59%-63% (58%-64% for FY10) — partly attributed to seasonal declines, partly to costs with ramping up 32nm manufacturing. ("Those early wafers tend to be pretty high cost products and as you have seen us do in prior transitions of new process technology we pretty quickly build inventory on the new stuff," CFO Stacey Smith noted during Intel’s analyst/investor Q&A .

And spending outlook for FY10:

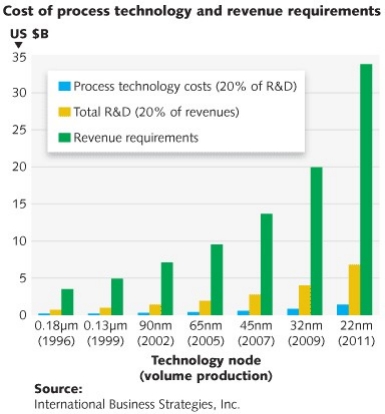

– Capex: $4.7B-$4.9B, up about 6% from $4.5B in 2009. (Intel’s early 2009 capex prediction started at $5.2B)

– R&D spending about $6.2B

Notable comments during the Q&A:

Inventories: "I expect to build a little bit more inventory in 1Q as I ramp 32nm products. It won’t be the same magnitude we saw this quarter but it will be up some. Then it starts looking a little more normal as it progresses through the year relative to demand." [CFO Stacey Smith]

"[…] Looking at our authorized channel those inventories are down and visibility into a lot of the OEM inventories and a lot of that is now held in our hub and what we see in the down channel so retail, the shipping lanes and stuff, what we see is a healthy level of inventory relative to the demand we see out over the next couple of quarters." [Smith]

"We are in the sweet spot of [factory] loading. We are running nicely full. We have the ability to respond to some upside. We always want to have some of that but we are full to the point we are getting really good cost results. I would expect that to be the norm for this year." [president/CEO Paul Otellini]

"What we are doing with this cycle in general is using the technology to move 32 nm into the mainstream more quickly than we did with 45. The rate of crossover between 32 and 45 will be more a function of second half demand in total than capacity planning to cut one off versus the other. If demand is red hot the transition will be slower even though we will ramp 32 as fast as possible and if it less red hot it will be slower." [Otellini]

Capital spending: "As a result of capital reuse and achieving efficiencies we were able to ramp 32nm process technology and still bring down our capital forecast from our expectation at the beginning of the year." [Smith]

"[…] We are making some investments in R&D projects this year. We have had five years in a row of year-over-year employment decline. We will actually grow employment a little bit in 2010. So you haven’t seen that from us in a long time. We have some high return on investment projects where we are going to go and make some incremental investments." [Smith]

What analysts say:

Craig Berger, FBR Research: There are likely two small issues for investors here. First, management’s 2010 gross margin guidance of 61% seems conservative vs. its 61% guidance for 1Q10 and versus the 65% Intel just reported. We believe management could raise this annual margin target later this year. Second, internal inventories went up, largely due to valuing 32nm inventory, but also due to management’s view internal inventories are too low. With another planned increase in internal inventories in 1Q, the bears may say this is the beginning of the end of this cycle for Intel. We respectfully disagree with those sentiments.

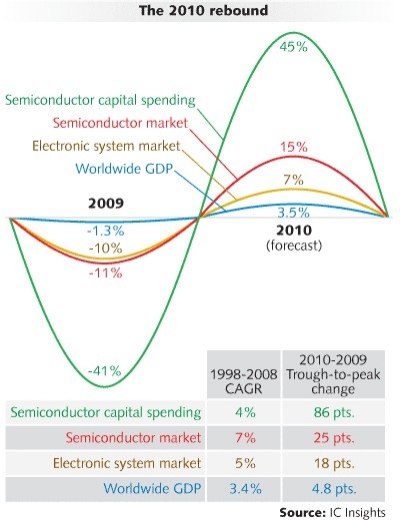

Ben Pang, Caris & Co.: "The strength of Intel’s core business bodes well for the anticipated capital spending rebound in 2010 and beyond." […] KLA should benefit from the more stringent defect requirements [for Intel’s latest silicon technology], while both NVLS and VSEA have demonstrated strong market share position at Intel."

Doug Freedman, AmTech Broadpoint: "We believe the gross margin impact on INTC’s manufacturing efficiencies at 300mm continue to be underestimated. […] We note that capex increased only 7% Y/Y to $4.8B despite China fab investments. […] We believe that FY10 gross margin guidance of 61% ±3% (the same level as 1Q10) is conservative given higher revenue levels and ramp down of 32nm start-up costs."

Meldrum did sound one cautionary note: He said that after major recessions in the past, the US government has created a "super-regulatory" institution, pointing to the Federal Research Board in 1907 and the SEC in 1929. He believes the creation of another such institution is possible, but if that happened it would only aid the semiconductor industry by stabilizing markets that are heavy consumers of electronics.

Meldrum did sound one cautionary note: He said that after major recessions in the past, the US government has created a "super-regulatory" institution, pointing to the Federal Research Board in 1907 and the SEC in 1929. He believes the creation of another such institution is possible, but if that happened it would only aid the semiconductor industry by stabilizing markets that are heavy consumers of electronics.