June 9, 2011 — Yole Développement’s "Thin Wafer Manufacturing Equipment & Material Market" research study found at least 10 methods currently in use to temporarily bond wafers, protecting thinned wafers during processing.

|

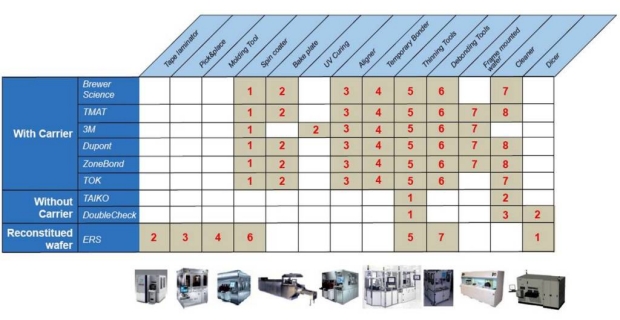

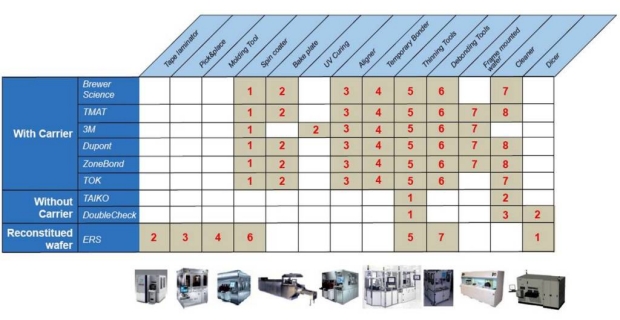

| Figure. Temporary bonding tools used during a temporary bonding step. The figures in red show the order of the steps. Source: Yole, Thin Wafer Manufacturing Equipment & Materials Markets Report, June 2011. |

Many consumer applications will require ultra-thin semiconductor wafers (down to 50µm) for advanced packages with through silicon vias (TSV), interposers, or fan-out wafer-level packaging (FOWLP); power devices like IGBTs, RF devices, and LEDs. Because ultra-thin wafers are less stable and more vulnerable to stresses than traditional ones, and die can be prone to breaking and warpage during grinding and wafer processing, new temporary bonding technologies will be required for handling support.

Wafer bonding tapes are unsuitable for ultra-thin wafers: they cause non-uniformity, can impact flexing, etc.

Yole has identified at least 6 carrier-based temporary bonding technologies — each with variations in chemistry, carriers, etc. Add to that carrier-free adn reconstituted wafer technologies, and the options are 10 or more. The market is so young, and no options are clearly winning out over others, says Dr Eric Mounier, Project Manager at Yole Développement, which means the technology developers are competing to win converts.

|

Companies mentionned in the report:

3M, ABB, Accretech, AIT, All Via, ALSI, AMAT, Brewer Science, Corning, Danfoss, Denka, Disco, DoubleCheck Semiconductors, Dupont, Dynatex, ERS, ESI, EVG, Fairchild, FhG IZM, Fico, Furukawa, Hamamatsu, Hitachi Chemical, Infineon, Invensense, IR, Jenoptik, Laserod, Leti, Lintec, Loadpoint, Lumileds, Mitsui Chemicals, Nitronex, Nitta, Nitto Denko, OnSemi, Osram, Panasonic, Plan Optik, ProTec, PVA Tepla, RFMD, Ricmar, Rorze, Schott, Scrypt, Sekisui, Shibuya, ShinEtsu, Skyworks, STM, Strasbaugh, Sumitomo Bakelite, Sumitomo Chemical, SUSS MicroTec, Synova, Sysmelec, Takada, TEL, TMAT, TOK, Triquint, Veeco, Yushin

|

The goal is temporary wafer bonding at a low cost, with high temperature resistance and no or little topographic issues. Tool makers, chemistry providers, and substrate suppliers are all working together in various ways to reach that goal. A few — Nitto Denko, TOK or TEL — are attempting to be a process and chemistry provider.

Yole expects the temporary bonding market to experience 5x market growth 2011 to 2016, raising its value to $300 million. Wafers that require temporary bonding during processing will top 35M by 2016 (estimated across all wafer sizes).

"Thin Wafer Manufacturing Equipment & Materials Market" describes markets, applications and technologies for thin wafer manufacturing: temporary bonding markets, applications, descriptions and trends for wafer thinning and dicing. This report also includes a market analysis on temporary bonding materials (wax, glue, tapes, carrier wafers) associated with the temporary bonding technology.

Dr. Eric Mounier has a PhD in microelectronics from the INPG in Grenoble. Mounier is in charge of market analysis for MEMS, equipment & materials at Yole.

Yole Developpement is a market research and strategy consulting firm analyzing emerging applications using silicon and/or micro manufacturing. Learn more at www.yole.fr

Subscribe to Solid State Technology/Advanced Packaging.

Follow Advanced Packaging on Twitter.com by clicking www.twitter.com/advpackaging. Or join our Facebook group

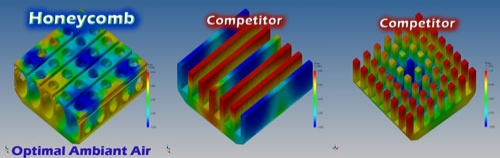

producing a steady flow of cool air inside the heatsink. Honeycomb heatsinks can be used with either plastic or metal/ceramic BGA packages, depending on the thermal interface material (TIM).

producing a steady flow of cool air inside the heatsink. Honeycomb heatsinks can be used with either plastic or metal/ceramic BGA packages, depending on the thermal interface material (TIM).

The orders were received during the third quarter of fiscal 2011 and are expected to ship in the second half of calendar 2011.

The orders were received during the third quarter of fiscal 2011 and are expected to ship in the second half of calendar 2011. In an exclusive series of blogs, imec reports from its International Technology Forum (ITF) last week in Brussels. Els Parton, science editor, imec, shares Jy Bhardwaj’s (Philips Lumileds) points about LEDs costs improvements.

In an exclusive series of blogs, imec reports from its International Technology Forum (ITF) last week in Brussels. Els Parton, science editor, imec, shares Jy Bhardwaj’s (Philips Lumileds) points about LEDs costs improvements.