by James Montgomery, news editor

July 26, 2010 – The issue of supply chain management came up in several keynotes, panels, and individual discussions at SEMICON West. "There’s a lot more focus on the supply chain," noted Applied Materials EVP/GM Randhir Thakur, in the Tuesday afternoon "Executive Panel." Litho tools have been getting attention as representing the worst of lead-times (9+ months, sometimes longer), but most process equipment has been straining to get product to customers — showing, more than anything, just how rapidly and completely things shut down a year ago, and how fast they’ve had to ramp back up again. (One story we heard: A major process tool firm had to pay a component partner’s delinquent electricity bill before engaging them in resupplying parts.) Thakur pointed out that some suppliers have simply shut their doors permanently.

The key, according to GlobalFoundries’ Tom Sonderman, is knowing how, where, and when to add capacity — i.e., predictability — to best manage capacity and ramp/slow as needed. That "bullwhip affects our suppliers even more so," noted fellow panelist Rick Wallace from KLA-Tencor. And one concern that comes out of this is whether quality suffers in a race to get products out the door. Lam Research now has stricter rules for its supplier base, said Steve Newberry: Lam cannot represent >40% of a supplier’s business, and the company actively pursues strategies such as multiple-qualified-supplier strategies where "basically we consider them as our own factory." Thakur agreed that quality is a fundamental issue as ramp cycles shorten — and here again, collaboration is key. "Our customers can do it; I think we in the wafer-fab equipment space can learn it," he said.

| More “lessons learned” from SEMICON West 2010: |

| Lesson #1: Good times here, for now |

| Lesson #2: Capital intensity & EUV |

| Lesson #3: 3D and packaging are hot |

| Lesson #5: Interests outside CMOS |

Litho has the poster child for chip tool lead-times, with reported delivery out to 9-12 months just a couple quarters ago. (It’s been suggested that Samsung’s capex surge may not only secure its own needs, but have the perhaps-not-unintended effect of keeping the critical tools out of the hands of others.) In just the past couple of months, orders in KrF tools have spiked, with lead-times rising to as much as 12 months, equal to immersion litho shipping schedules.

But things seem to be improving noticeably, due in large part to companies’ hard work to get leaner during the downturn. In the Bulls/Bears panel Q&A, Citigroup’s Tim Arcuri said ASML is on the brink of reducing lead-times to six months by September. And AMAT claims 60%-70% of its turnaround is turns business, added Goldman Sachs Jim Covello. "I’m shocked about lead-time reductions," he admitted, noting that there are more issues on the backend now. "We won’t see a level of double ordering this time." Lam’s Bagley pointed out that equipment suppliers’ lead-times always beat those of the facilities preparing to receive the tools — "it used to be a wash," he said.

That six-month lead time for immersion litho tools is actually a sweetspot, Barclays’ CJ Muse points out in his post-SEMICON West notes ("it takes 4+ months just to build a Zeiss lens). Samsung probably won’t get all the immersion tools it wants (e.g. its Austin fab may slip into 1Q11), he said. And while the NXT offers 30% better throughput, the growing number of critical layers for DRAM and logic/foundry mean more tools will be needed, not fewer, he points out.

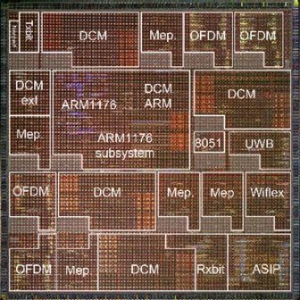

Power management has been a major optimization goal during the development of this chip. Based on the unique ANOC technology, 23 frequency islands can be programmed dynamically to ensure the best performance-versus-energy ratio. As a result, the circuit exhibits less than 500 mW for up to 40 giga operations per second (GOPS) performance, which is one of the best power efficiency measurements reported for a chip with a high level of flexibility.

Power management has been a major optimization goal during the development of this chip. Based on the unique ANOC technology, 23 frequency islands can be programmed dynamically to ensure the best performance-versus-energy ratio. As a result, the circuit exhibits less than 500 mW for up to 40 giga operations per second (GOPS) performance, which is one of the best power efficiency measurements reported for a chip with a high level of flexibility.