The Snapdragon 800 (Qualcomm MSM8974) is Qualcomm’s leading-edge, low-power, mobile phone app’s processor with built-in 3G/4G LTE modem, using the latest Krait 400 CPU rated at 2.3 GHz and their 450 MHz Adreno 330 GPU. It was launched at this year’s CES International with this rather slick commercial.

Significantly, it is fabricated using the TSMC 28HPM (28-nm, High-Performance Mobile) process, which extends TSMC’s high-k, metal gate (HKMG) processing into the mobile space. Before this, all Qualcomm’s mobile chips were made with the TSMC 28LP polysilicon gate/SiON process; and to our knowledge, this is the first volume production part using 28HPM.

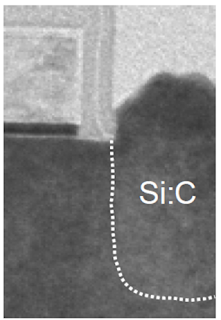

The 28HPM process sees a shrink in minimum gate lengths and SRAM cell size when compared with the 28HP process, and the inclusion of embedded SiGe source/drains for PMOS strain, which was not part of 28HPL.

|

| TSMC 28HPM PMOS transistor |

TSMC claims the technology can provide better speed than 28HP while giving similar leakage power to 28LP. The wide performance/leakage coverage apparently makes 28HPM ideal for applications from networking, tablet, to mobile consumer products.

The Rockchip RK3188 is targeted on tablets rather than phones, but it uses the GLOBALFOUNDRIES’ 28SLP (Super Low Power) process, their equivalent to TSMC’s 28HPM, aimed at mobile products. It is again a quad-core part, this time with ARM A9 CPUs running at 1.6 GHz, and quad-core ARM Mali GPUs rated at 600 MHz.

|

| Rockchip RK3188 floorplan showing some of the major functional blocks |

Rockchip has squeezed the functionality into ~25 sq. mm, less than a quarter of the size of the Qualcomm chip; not least because the A9 cores are noticeably smaller than the Qualcomm-designed Krait cores based on the ARM architecture, and of course there is no LTE.

GLOBALFOUNDRIES is obviously happy to have won the Rockchip business – their CEO Ajit Manocha specifically mentioned the partnership in his keynote talk at Semicon West:

The 28SLP process differs in a basic way from the TSMC 28HPM – GloFo is using their version of the Common Platform (GLOBALFOUNDRIES, IBM, Samsung) 28-nm process, which is a ‘gate first’ variety, i.e. a polysilicon gate is used with a HKMG stack at its base, doped to form NMOS and PMOS transistors. TSMC’s ‘gate last’ process uses a sacrificial polysilicon gate for all the processing up to the end of the source/drain processing, then the polysilicon is removed and replaced with distinct HKMG stacks which are tuned for NMOS and PMOS.

Like the other Common Platform HKMG processes, a SiGe channel is used in the PMOS transistors, though with GloFo’s own spin – none of these processes are the same from the different vendors.

Compared with the older 32-nm HKMG process used for AMD processors, the Rockchip uses bulk silicon, not SOI, and gate lengths, contacted gate pitches and SRAM cell size are shrunk, but in the same ballpark as TSMC’s process. There is no dual-stress liner or embedded SiGe source/drains to enhance PMOS performance, but this product is rated at 1.8GHz rather than TSMC/Qualcomm’s 2.3 GHz.

|

| GLOBALFOUNDRIES 28SLP PMOS transistor |

So we have two processes targeted at similar spaces, but with very different takes on how to do it. TSMC and Qualcomm are following the industry norm, supplying chips to a US company from Taiwan, and GLOBALFOUNDRIES and Rockchip have reversed the trend, supplying chips to China from the West, and it’s tempting to speculate they are from the Malta fab in New York.