By Dick James, Chipworks

Later this month, the good and the great of the electron device world will make their usual pilgrimage to San Francisco for the 2014 IEEE International Electron Devices Meeting. To quote the conference web front page, IEDM is “the world’s pre-eminent forum for reporting technological breakthroughs in the areas of semiconductor and electronic device technology, design, manufacturing, physics, and modeling. IEDM is the flagship conference for nanometer-scale CMOS transistor technology, advanced memory, displays, sensors, MEMS devices, novel quantum and nano-scale devices and phenomenology, optoelectronics, devices for power and energy harvesting, high-speed devices, as well as process technology and device modeling and simulation. The conference scope not only encompasses devices in silicon, compound and organic semiconductors, but also in emerging material systems. IEDM is truly an international conference, with strong representation from speakers from around the globe.”

That’s a pretty broad range of topics, but from my perspective at Chipworks, focused on the analysis of chips that have made it to production, it’s the conference where companies strut their technology, and post some of the research that may make it into real product in the next few years.

In the last few days I’ve gone through the advance program, and here’s my look at what’s coming up, in more or less chronological order. As usual there are overlapping sessions with interesting papers in parallel slots, but we’ll take the decision as to which to attend on the conference floor.

Saturday/Sunday

Again this year the conference starts on the Saturday afternoon, with a set of six 90-minute tutorials on a range of leading-edge topics:

- Physical characterization of novel materials and devices for logic and memory, W.Vandervorst, imec

- Power Semiconductor Device Basics: History, Application, and Physics, Ichiro Omura, Kyushu Institute of Technology

- Optoelectronics of Graphene and other 2D materials, Phaedon Avouris, IBM Research, T.J. Watson Research Center

- Reliability characteristics of CMOS transistors post Si/SiO2/poly-Si gate stack scaling, Eduard Cartier, IBM Research, T.J. Watson Research Center

- Power Electronics for a Smart Energy Future, Johan Driesen, KU Leuven, ESAT-ELECTA

- Nonvolatile Memories: old and new, Jan Van Houdt, imec

The first three are from 2.45 – 4.15, and the remainder from 4.30 – 6.00. This year I hope to make it to my old friend Wilfried Vandervorst’s session on characterisation, and possibly the other imec tutorial on memories at 4.30.

Wilfried gave an impressive talk at the imec symposium at Semicon West, and this time he has an hour and a half instead of 45 minutes, so hopefully a good bit more detail on what we can see, now that we are counting atoms in transistor analysis.

On Sunday December 14th, we start with the short courses, “Challenges of 7nm CMOS Technologies” and “3D System Integration Technology”. Last year the short course was “Challenges of 10nm and 7nm CMOS Technologies”, so I guess we’ve moved on a bit; though I still need convincing that the 10-nm process architectures are locked down as yet.

Hidenobu Fukutome of Samsung has organised the former, and we have some impressive speakers – Greg Yeric, Senior Principal Design Engineer of ARM, (Circuit application requirements), Peide Ye, Purdue University (Device challenges), Guido Groeseneken, KU Leuven & imec, (Reliability challenges), Eric Karl, Intel, (On-die memory challenges), and Tsutomu Tezuka, Advanced LSI Technology Laboratory, Toshiba (Process and integration challenges). With 14-nm product on the market now, we need to look ahead, so this is appropriate – on the Intel clock, 7-nm is only four – five years away!

It now seems that 10-nm will be silicon-based, so we’ll see what the guys predict for 7-nm; new channel materials, nanowire transistors, and how will they integrate into a manufacturable process? What will be the effects on the performance of the basic logic blocks? What will device reliability be like with the potential new materials/structures? Hopefully we’ll find out here!

Eric Beyne of imec has set up the other short course; 3D is a very hot topic these days, both finFET and die stacking – here we are talking about die stacking.

Denis Dutoit of Cea-Leti looks at 3D System Design – Challenges for 3D Integration; I have the distinct impression that the manufacturing technology is in place, but design and test still have a way to go.

Next up is Kangwook Lee, Tohoku U, on Enabling Technologies: TSV Technology; again TSV technology is being promoted as here by both foundries and OSATs, and some products such as the Xilinx 2.5D FPGAs are out there, and stacked memories such as the Hybrid Memory Cube are sampling.

After lunch we have 3D evangelist extraordinaire Subu Iyer from IBM, talking about Enabling technologies: 3D integration for the Memory subsystem. IBM has been embedding DRAM into their products for several generations now, and as noted above, we are starting to see 3D-packaged memory come on to the market.

Wafer-to-wafer bonding is an essential part of 3D stacking, and that’s the topic of James Lu from Rensselaer Polytechnic. The last session is on 3D Reliability and Impact of 3D Integration on Devices, with Kristof Croes of imec discussing the device effects of the additional processing needed to make a 3D stack.

So some good solid stuff – although the courses make a long Sunday, from 9 a.m. to 5.30 p.m., but it’s worth sticking around to the end.

Sunday evening has some extra sessions; Sematech is holding a session on “Materials & Technologies for Beyond CMOS” at an as-yet unnamed location; and Leti will host a workshop on their “vision for silicon nano-technologies in the next 10 years” from 5.30 – 8.30 pm at the Nikko Hotel, across the street from the Hilton.

Monday

Monday morning we have the plenary session, with three pertinent talks on the challenges of contemporary electronics:

- SiC MOSFET Development for Industrial Markets, John Palmour, Cree Inc. – broadening the range of uses for silicon carbide?

- Are 3D atomic printers around the corner? Enrico Prati, CNR IMM (Italy’s Institute for Microelectronics and Microsystems) – now that 3D printers are becoming consumer goods, can we push the idea into the atomic scale? That sounds like the potential for everything from drugs design to the ultimate version of Moore’s law..

- Research into ADAS with Driving Intelligence for Future Innovation, Hideo Inoue, Toyota – Automated Driver Assistance Systems; moving towards the self-driving car?

After lunch we have seven parallel sessions coming up!

Session 2 is a focus session on power devices, with a kick-off paper by John Baliga of NCSU, on the Social Impact of Power Semiconductor Devices (2.1). John invented the IGBT in his time at GE back in the 80’s, and claims that the technology has reduced global carbon dioxide emissions by 75 trillion pounds over the last 30 years. He speculates that this can only increase with the introduction of new power devices. Papers 2.3 – 2.5 and 2.7 look like reviews of high-power switch technologies, and Si-, SiC and GaN-based power devices, respectively, while 2.2 and 2.6 look at specific SiC JFET and GaN HEMT devices.

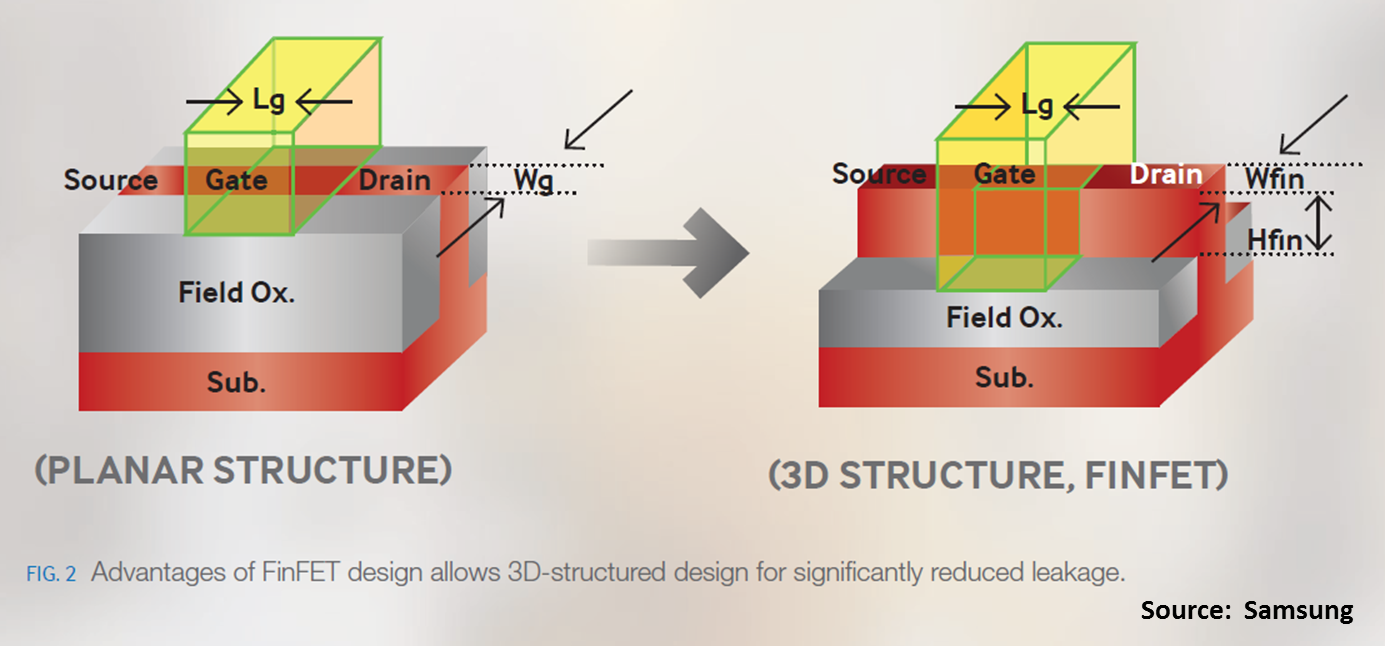

Session 3 is the hot Advanced CMOS Technology group of papers with late news additions by Intel (3.7) and IBM (3.8), both on 14-nm finFET technologies, which even triggered their own press release.

The Intel finFET (note – not trigate!) device features “a novel subfin doping technique” to minimise fin doping and leakage under the fins, and air-gaps in two metallisation levels. This is the first use of air-gaps in a production logic part that I know of; we’ve seen them in memory chips for a while. Intel had a persuasive paper on this at the 2010 IITC conference [1], and I was wondering if we would see implementation at this node.

If you hunt hard in Intel’s August 14-nm announcement, you can find the air-gaps in the M5 level:

And we did find them in the M5 and M7 levels, but I will leave any detailed comment until a later blog. The IITC paper [1] speaks of using a mask step to define specific air-gap locations, and we can confirm that masking has indeed been used to define specific locations.

Now that we are analysing the Intel part, it would be remiss of me not to show an early shot of the fins, and they are clearly different from the 22-nm variety. There has been an obvious reduction in the width of the fin from its initial etched dimension, and it is tempting from this image to say that the NMOS fin is wider than the PMOS, but again more thorough discussion will have to wait.

IBM’s finFET is on SOI (of course, this is IBM!) and has a “unique dual workfunction process” which allows multi-Vt versions of both NMOS and PMOS, and claims sub-20 nm gate lengths. The process also includes fifteen metal layers and the latest version of their e-DRAM technology.

With all the Intel/IBM hype, I have become out of order here, because paper 3.1 from TSMC discloses what looks like their 16FF+ 16-nm finFET technology, advanced from the 16FF reported last year. A 15% speed boost and 30% power reduction is claimed, or 40% speed gain and 60% power saving compared to the 20-nm process.

Gossip in the industry has it that 16FF was not advanced enough for TSMC’s customers, so they did some transistor engineering and cranked up the performance; 16FF is not even mentioned on the website these days, and 16FF+ is now in risk production, with endorsements by Avago, Freescale, LG Electronics, MediaTek, Nvidia, Renesas and Xilinx, .

It will be interesting to see if any of the dimensions have changed from the 48 nm fin pitch and 90 nm contacted gate pitch announced last year. The metal stack is stated to be the same as the 20-nm planar process with a 1x pitch of 64 nm.

Paper 3.2 is from Avago, discussing Analog Circuit and Device Interaction in High-Speed SerDes Design in 16nm FinFet Process, and Renesas presents 3.3, on 16-nm 6T SRAM macros, both presumably TSMC’s process. 3.4 again looks at SRAM, but this time on STMicroelectronics’ 28-nm UTBB FDSOI process.

Next up is a couple of academic papers (3.5 & 3.6), discussing a 28-nm integrated RF power amplifier, and a 3D-stacked light harvester on a “epi-like Ge/Si monolithic 3D-IC with low-power logic/NVM circuits”.

3.7 and 3.8 are the Intel and IBM papers, and 3.9 is another late-news paper, from STMicroelectronics, but a change of pace from the finFETs – a 55-nm SiGe BiCMOS technology this time.

And by now it’s 5pm, the end of an intense afternoon!

In session 4, we take a look at Display and Imaging Systems. STMicroelectronics starts us off discussing MOS Capacitor Deep Trench Isolation for CMOS Image Sensors (4.1) in a joint talk with CNRS and CEA-LETI.

One of the goals in image sensors has to be integrating the A/D converters on each pixel, instead of at the edge of the pixel array, and 3D stacking comes to images sensors in paper 4.2 from NHK and U Tokyo; in which SOI wafers are direct bonded so as to provide each pixel with A/D conversion.

However, we won’t be seeing this in a phone anytime soon, as it is a proof-of-concept with 60-µm square pixels, as opposed to the 1-2 µm pixel pitch in most phone cameras.

NHK (jointly with Panasonic and U Hyogo) has another stacked sensor in 4.3, this time a selenium photodiode stacked on CMOS circuitry.

The remaining four papers are academic, covering far-infrared (4.4), a stacked SOI multi-band CCD (4.5), an embedded CCD in CMOS (4.6), and the display paper is 4.7, a solid-state incandescent device.

Session 5 covers Nano Device Technology – 2D Devices, a research session; 5.5 is a review of Nanophotonics with two-dimensional atomic crystals; the other papers all cover graphene devices (5.3, 5.4 and 5.6), black phosphorus (5.2), and molybdenum disulphide and tungsten diselenide (5.1, 5.7).

Resistive RAM is discussed in session 6. CEA-Leti has three papers in the afternoon, (6.1, 6.3, 6.5) The first (joint with Altis Semi) looks at oxygen vacancies in doped oxide/Cu-based conductive bridge RAM (CBRAM), improving the Cu filament formation in the resistive layer; 6.3 is an invited paper that takes a higher level view of CBRAM and OxRAM devices in two different applications; and 6.5 is a detailed examination of CBRAM operation.

Micron and Sony get together to build a 27-nm 16Gb Cu-ReRAM part in 6.2, with a 1T 6F2 cell – definitely some DRAM technology showing up here, in the buried wordlines:

TSMC and National Tsing Hua U have a 28-nm BEOL RRAM in 6.4; Stanford U looks at thickness limits in HfO-based RRAM in 6.6; Crossbar (6.7) discusses crossbar RRAM arrays; and imec/KU Leuven finishes the session with a paper on a TiN/Si/TiN selection device for RRAM switching elements (6.8).

Modeling Simulation of Extremely Scaled Group IV and III-V FETs is the topic in session 7, looking way ahead.

In paper 7.1, imec and Synopsys look at the stress effects of 3D stacking on 7-nm devices(!); 7.2 examines mobility enhancement in sub-14nm FDSOI, by the CEA-Leti/STMicroelectronics/IMEP/IBM/SOITEC FDSOI crew; and transient electrothermal effects in nanoscale FETS are considered in 7.3., from Osaka U and Kobe U, and JST-CREST.

Victor Moroz (Synopsys) does a comparative analysis of 7-nm finFETs in different materials in 7.4 – this might be a follow-up of his talk at Semicon West back in July, in which he concluded that silicon is still the best channel material, at least for low-power mobile devices.

Samsung and Udine U also look at different material nFinFETs (7.5, 7.6), and Peking U discusses III-V ultra-thin body pMOSFETs in the last paper of the session (7.7).

NEMS (Nanoelectromechanical Systems) and Energy Harvesters are dealt with in Session 8 – six academic papers, ranging from graphene and Mo disulphide atomic-scale layers that vibrate at RF frequencies (8.1), to photoelectric hydrolysis on MIS photocathodes (8.6).

For those interested in energy storage, Intel have fabricated porous silicon capacitors (8.2) that can potentially be integrated on-die or onto solar cells, taking advantage of the extreme conformal deposition capabilities of atomic-layer deposition (ALD). The image below shows a top-down view of the porous silicon before and after ALD TiN deposition; the wall of the pore walls get thicker, but the pore structure doesn’t change. Capacitances of up to 3 milliFarads/cm2 are claimed.

Then in the evening we have the conference reception at 6.30, through until 8 pm.

Tuesday

In the morning we have another seven parallel sessions, starting with session 9 on Advanced CMOS Devices for 10nm Node and Beyond, so another one I will definitely be targeting.

The first paper (9.1, from IBM/STMicroelectronics/SOITEC/CEA-Leti) is about strained 10-nm FDSOI devices, incorporating “a fully compressively strained 30% SiGe-on-insulator (SGOI) channel PFET on a thin (20nm) BOX substrate”; they also report ‘strain reversal’ in a PFET – is that so much strain that it reduces mobility? In their workshops at last year’s IEDM and Semicon West, CEA-Leti have been showing a roadmap that jumps from 28-nm to 14-nm and then 10-nm nodes – this looks like the first showing of the 10-nm technology.

That is followed (9.2) by an invited talk from Simon Deleonibus of CEA-Leti on how process technologies can move us towards the zero-power era(?).

Purdue U claims the First Experimental Demonstration of Ge CMOS Circuits (9.3) on a GeOI substrate, while TSMC details InAlP-capped Ge nFETs on Si and Ge substrates (9.4), and Ge n-finFETs on Si (9.5). Still in germanium, National Taiwan U talks Ge nanowire nFETs on SOI (9.6).

The last paper of the session (9.7) is from AIST in Japan on tunnel finFETS in a CMOS process.

Session 10 is a focus session on Novel Imagers and Specialty Imaging Applications, starting with an invited talk by Jiaju Ma (10.1) from the Thayer School of Engineering at Dartmouth, on the Quanta image sensor; as near as I can make out, this type of sensor scans the pixel array so fast that it effectively reads individual photoelectrons, and the image is formed by integrating x, y, and time.

Paper 10.2 from TU Delft discusses single-photon avalanche diodes (SPADs), which have enabled solid state range finding, fluorescence lifetime imaging, and time-of-flight positron emission tomography. The topic of 10.3 (Ritsumeikan U, TU Delft, Osaka U) is high-speed image sensors, aiming for one giga-frame per second!

Another invited talk is by Siemens (10.4), about organic photodetector imaging, and next imec details a CMOS-compatible approach to hyper- and multispectral imaging (10.5).

In a different spin, Annette Grot of Pacific Biosciences (10.6) will discuss how high-resolution, low-noise and high-speed image sensors have enabled large amounts of DNA to be sequenced quickly and at reduced cost; and how further advances will keep on pushing productivity and cost reduction.

For the final talk, we go from chip-scale to huge – the large scale hybrid pixel detector systems used at the Large Hadron Collider experiments at CERN (10.8).

Session 11 is the second group of talks about power and compound semi technologies, this time on High Voltage and RF Devices. Five of the six papers are on GaN devices, and one (11.2) describes a diamond MOSFET good up to 400C. We have a new acronym in there – a SLCFET (Super-Lattice Castellated Field Effect Transistor), with a 3D castellated gate structure (11.5) – that should make for a couple of interesting slides!

Circuit/Device Variability and Integrated Passives Performance is the focus of session 12; the middle papers, 12.3 and 12.4 are the passives talks, on Ultra-High-Q Air-Core Slab Inductors (IBM), and Above CMOS Integrated High Quality Inductors for wireless power transmission (HONG Kong UST). The other discussions range from finFET simulations (12.1 and 12.2) through MTJs for random number generation (12.5), noise suppression by using dynamic threshold voltage MOSFETs (12.6), and finally a consideration by ARM of poly pitch co-optimization in standard cells below 28-nm (12.7).

We look ahead to TFETs and other Steep-Swing Devices in session 13. The first paper (UCal Berkeley, Toshiba) discusses a nano-mechanical relay (13.1), which inherently has zero off-state leakage and perfectly abrupt ON/OFF switching behavior, but also serious manufacturing challenges. 13.2 and 13.3 are TFET talks, the 13.4 topic is a Schottky-barrier Si FinFET, and 13.5 and 13.6 review piezoelectric negative differential capacitance effects and devices.

Advanced Memories and TSV are the subjects of session 14; the first four papers are more resistive RAM, from imec (14.1 and 14.2), Politecnico di Milano/Micron (14.3) and Politecnico di Milano/Adesto (14.4). Adesto is the only company I know actually selling CBRAM parts, although we haven’t had a chance to look at them yet.

14.5 is a follow-up paper looking at noise in Samsung’s V-NAND flash [2], and 14.6 is also a follow-up from IBM on mobile ion penetration from BEOL layers close to TSVs. IBM’s TSV process uses MEOL connection to the TSVs [3], so it’s feasible that there could be some cross-contamination. Tohoku U contributes the last discussion (14.7), testing polyimide TSV liners as a way of reducing the stress in the adjacent silicon.

More sensors and MEMS papers in session 15; the first three are from Tsinghua U, about different applications of graphene MEMS (15.2 also from Berkeley), and TSMC/U Illinois contribute 15.4, on an integrated 180-nm SOI-CMOS biosensor.

A*STAR in Singapore author the final two papers, but on very different topics. 15.5 is an optical biosensor with Ge photodetectors built in to the back end, and 15.6 details a MEMS-tunable laser combined with a photonic IC.

The speaker at the conference lunch will be T.J. Rodgers, founder, President and CEO of Cypress Semiconductor, a well-known voice in the business for decades. Given the recent news of the merger between Cypress and Spansion, he could be an illuminating speaker!

Session 16 focuses on Ge and SiGe Transistors, starting with an IBM/GLOBALFOUNDRIES report (16.1) on strained SiGe-OI finFETs with 50% Ge and fin width of 3.3 nm and gate length of ~16 nm; clearly aimed at the 10-nm node.

Looking a bit further into the future, CEA-Leti/STMicroelectronics/SOITEC (16.2) examine omega-gate CMOS nanowires, with strained SiGe-channel p-FETs and Si-channel n-FETs, integrated into a SOI-CMOS process. From the look of the pictures below they are using a gate-first approach, so there is still some life in that technology.

16.3 is another nanowire paper from National Tsing Hua U, this time with dopant-free Ge junctionless nanowire non-volatile memories as well as Si nanowire FETs; and 16.4 is a study of Ge quantum-well finFETs fabricated on a 300mm bulk Si substrate, from Penn and N. Carolina SUs with TSMC and Kurt Lesker Co.

Imec tries out replacement metal gates on Ge n-finFETs with raised NiSiGe source/drains in 16.5; AIST examines poly-Ge-OI junctionless p- and n-finFETs, fabbed by flash annealing in 16.6; and Purdue U (16.7) reports on GeOI CMOS devices with recessed S/D.

Session 17 looks at Trapping Mechanisms in AlGaN/GaN Transistors; definitely at the academic end of the scale for me, although the last paper, CMOS-Compatible GaN-on-Si Field-Effect Transistors for High Voltage Power Applications, by TSMC, seems a bit out of place (17.6).

Session 18 is the second one on circuit/device interaction, this time considering Analog and Mixed Signal Circuits. Xilinx studies the interaction between devices and analog circuits used in high-speed transceivers in both planar and FinFet processes in 18.1. Part of this will be using the TSMC 16-nm finFET process, we’ll see if it adds anything to their paper in session 3.

Broadcom looks at mismatch in HKMG transistors related to the layout, and finds sensitivity to top metal routing, in 18.2. GLOBALFOUNDRIES (18.3) looks at Analog and I/O Scaling in 10nm SoC Technology and Beyond; is it better to take an increasing proportion of the die for hard-to-shrink analog, or go with TSVs and multiple dies?

CEA-Leti has a pathfinding paper (18.4) reviewing RF front-end modules (FEMs) in the light of the increasing number of modes (GSM, WCDMA, LTE, etc) and frequency bands in mobile devices. There are now more than 40 bands worldwide, so we see multiple FEMs in the worldphones we take apart, and keeping costs down while enhancing capability is one of the understated challenges in the industry.

There is more RF from Mediatek in 18.5, this time examining Digitally-Intensive RF Transceivers in Highly Scaled CMOS; apparently, these days embedded intelligence is needed on-chip to reduce the sensitivity of circuit performance to device characteristics.

The last paper in the session (18.6) is from Keio U, discussing circuit/device interaction in the 3D context of inductive coupling between dies.

Session 19 is the third memory session, this time on MRAM, DRAM and NAND; the first three talks are focused on STT-MRAM, from imec (19.1), Hanyang U/Samsung (19.2), and LEAP (19.3). Then IBM updates on their embedded DRAM (19.4), now at the 22-nm node in their latest Power8 processor (which, being IBM, is ~650 sq. mm!).

TSMC discusses a new Self-Aligned Nitride non-volatile memory cell in 19.5, and Macronix updates us on their BE-SONOS charge-trapping NAND flash (19.6) in the last paper of the session.

Characterization and Reliability of Advanced Devices is the subject of Session 20; papers 20.1, 20.3, and 20.5 all deal with nanowire characterization; imec has two studies, on HKMG InGaAs finFETs (20.2), and ESD diodes in Si finFETS (20.4); and finally two invited reliability presentations, by Jim Stathis of IBM (20.6) and Tony Oates of TSMC (20.7), on what the challenges are in their field as we move beyond 14/16 nm.

Session 21 is a group of five papers discussing Atomistic Modeling of Device Interfaces and Materials, the first being a multi-national study of hole traps in p-MOSFETs (21.1); I had not realized that such traps had similar characteristics in different oxide dielectrics, whether it be silicon or high-k; and it appears that hydroxyl (-OH) groups could be the cause.

The next three talks (21.2, 21.3, 21.4) are also dielectric and interface studies, as is the last, but 21.5 is focused on HfO and HfAlO-based RRAM.

We go back to MEMS in session 22, actually NEMS as well, as in 22.1, which is a review of integrating NEMS with CMOS (U Grenoble Alpes, CEA-Leti, MINATEC), and 22.4, another CEA-Leti talk on polySi nanowire sensors. Tsing-hua U has two papers also, 22.2 on a nanomechanical thermal-piezoresistive oscillator, and 22.3 on CMOS-MEMS Oscillators. The final two presentations are from A*STAR, about integrating RF MEMS resonators and phononic crystals (22.5), and a 9 degree of freedom capacitive sensor.

That brings us to the end of the afternoon, and Applied Materials is hosting a panel on “The Transistor Revolution” in the Nikko Ballroom in the Nikko Hotel. In parallel Coventor is hosting an event “Survivor, Variation in the 3D Era” in the Carmel Room, also at the Nikko Hotel. They both usually cater us well, so once we’re sated from the hospitality we can wander back to the Hilton for the conference evening panel:

“60 Years of IEDM and Counting: Did we push silicon based devices for integrated electronics to the ultimate and what does the future hold?”

Usually there are two panels, having one avoids conflicts this year; and there are some distinguished panelists – Krishna Saraswat from Stanford University, with two colleagues, Yoshio Nishi and Philip Wong, Chenming Hu (UCal Berkeley), Hiroshi Iwai Tokyo Institute of Technology), Jesus del Alamo (MIT), and Kurt Petersen, co-founder of six MEMS companies, and a member of the Band of Angels.

Wednesday

Wednesday morning has sessions 25 – 31; S25 on III-V for Logic; MIT has two papers, on InGaAs Quantum-Well MOSFETs (25.1), and InGaAs/InAs heterojunction single nanowire vertical tunnel FETs (25.5).

25.2 is an invited review of “High-Performance III-V Devices for Future Logic Applications”, by Dae-Hyun Kim of GLOBALFOUNDRIES; 25.3, by IBM, is more high-performance self-aligned InGaAs-channel MOSFETs; 25.4 (UCal, Santa Barbera) is also InGaAs, but with InP Recessed Source/Drain Spacers; and 25.6 discusses an InAlN/AlN/GaN triple T-shape fin-HEMT (Nanyang TU, Ohio State U, Institute of Materials Research and Engineering).

S26 covers Thin Film Transistors for Display and Large Area Electronic Applications. Imec demonstrates an ultra-low power organic 8 bit transponder chip in 26.1, followed by IBM with heterojunction field-effect thin-film transistors (TFTs) with crystalline Si channels, and gate regions comprised of hydrogenated amorphous silicon or organic materials (26.2).

CBRITE is next up (26.3), on High Performance Metal Oxide TFTs, then a change of pace to carbon nanotubes with sputtered and spray-coated.

Metal oxides to form complementary inverters, from the Swiss Federal Institute of Technology, Imperial College London, and U Würzburg (26.4).

Believe it or not, Delft U has worked out a way to put silicon TFTs on paper or other soft substrates:

“The Delft team made the devices by casting a quantity of liquid polysilane onto a substrate, and forming a thin film from it by “doctor-blading,” or skimming it with a blade. High-performance polysilicon channel regions then were formed by laser annealing, using short pulses of coherent light to selectively crystallize the disordered film. The maximum temperature required was only 150ºC, making the TFTs suitable for paper and plastic substrates such as PET and PEN.” (26.5)

Tsing Hua U finishes up the session with the last two papers – a study of “Ultra-Thin Body (2.4nm) Poly-Si Junctionless Thin Film Transistors with a Trench Structure”, claimed to be useful for displays and 3DICs; and more poly-Si channel junctionless FETs, but this time with a poly fin (26.6, 26.7).

Hybrid and 3D Integration is the topic of Session 27; TSMC starts off with a review paper about wafer-level system integration technologies (27.1), followed by Nikon, demonstrating their precision-aligning Cu-Cu bonding system for 3DICs (27.2); then TSMC adds high-k metal-insulator-metal capacitors to their CoWoS interposers (27.3).

Stanford U pushes the boundaries in paper 27.4 by integrating traditional silicon-FETs with RRAM and carbon nanotube-FETs, to form four vertically-stacked circuit layers (logic layer followed by two memory layers followed by a logic layer).

CEA-Leti has been working on monolithic 3D integration for a while, and here they consider the thermal budget of the bottom layers (27.5). The last paper has KAIST transferring SOI silicon nanowire SONOS memory onto a plastic substrate, after thinning down to the buried oxide (27.6).

We have more emerging memory papers in session 28, together with a couple on heterogeneous integration. Toshiba starts the session discussing high density STT-MRAM for cache memory (28.1), using MTJs embedded in the back-end stack. Tohoku U and NEC look at hybrid MTJ/CMOS logic in 28.2 to make ultra-low-power logic LSI, and Rambus investigates surge current control in RRAM arrays in 28.3.

Paper 28.4 is a CEA-Leti (et al.) study of pattern recognition using convolutional neural networks made from HfO2 based OxRAM devices as binary synapses. National Chiao Tung U is also researching synaptic use of RRAM for neuromorphic computation in 28.5.

Tohoku U returns with a 3-D stacked multicore processor module made from a 4-layer 3-D stacked multicore processor chip and a 2-layer 3-D stacked cache memory chip (28.6), and using backside TSVs to enable multichip-on-wafer 3D integration. Below is an X-ray tomograph of the TSV stacks, the processor on the left and the memory on the right:

In 28.7, Penn State U et al. demonstrate coupled hybrid vanadium dioxide FET oscillators in a platform for associative computing, claiming ~20x power reduction compared with CMOS; and the last paper from UCal Berkeley (28.8) integrates NEMS into a CMOS back-end stack for ultra-low power applications.

Session 29 continues the memory theme, discussing PCM and Neural Networks, and kicked off (29.1) by Micron Italy (et al.) looking into different GeSbTe PCM cell architectures.

29.2 is from the Japanese LEAP consortium, describing a new type of PCM, “topological-switching random-access memory,” (TRAM). It differs from conventional PCM in that the latter works by the rapid heating of a chalcogenide material, which shifts it between its crystalline and amorphous states; whereas TRAM stores data by movement of germanium atoms within a GeTe/SbTe crystal superlattice:

The authors claim up to 20x reduction in programming energy, achieving a set/reset current as low as 55 µA.

We have an invited paper in 29.3, “Phase Change Memory and its Intended Applications”, by Chung Lam of IBM, followed by a statistical study of PCM to optimize memory capacity (29.4, UCal Berkeley et al.). We get back to PCM-based neural networks in 29.5, again from IBM, and Politecnico di Milano/Micron look at PCM set-transition energies (square vs triangular pulse) in 29.6.

IBM again takes the podium in 29.7, examining access devices for crossbar resistive memories, and they are a co-author with Macronix and National Tsing Hua U in the last paper, detailing a PCM recovery method – apparently a local anneal can be done on-chip to recover the phase-change properties if they degrade due to too many cycles (29.8).

Simulation of Novel Materials and Devices for FETs are considered in session 30; Toyota Tech Institute, Osaka U, and U Tsukuba (30.1) show that random dopant fluctuation in the source region causes a noticeable variability in the on-current of Si nanowire transistors, and its impact is found to be much larger than that of random telegraph noise (RTN).

30.2 is a review of Tunnel-FETs for future low-power technology nodes, by imec; 30.3 (U Florida) simulates Mo-disulphide-WTelluride vertical tunneling transistors; 30.4 (ETH Zurich) is another Mo-disulphide transistor study, as is 30.5, but also evaluates W-diselenide (UCal Santa Barbara); and the session finishes with a simulation of a (B-N) co-doped graphene TFET by Hong Kong UST/NanoAcademic Technologies (30.6).

The last focus session is session 31, Sensors, MEMS, and BioMEMS. It opens with a display of bio-MEMS for handling single molecules, including silicon nano tweezers, arrays of micro chambers, and chips with linear bio molecular motors (31.1, U Tokyo). The specific application is the use of MEMS technology on the molecular scale to conduct studies of DNA degradation and protein mutation related to Alzheimer’s disease. MEMS tweezers were used to trap bundles of DNA molecules to study them for stiffness and viscosity, which are markers of DNA degradation. Here we have an electron microscope image of a DNA molecular bundle between the tips:

Next up, U Bologna/U Southampton research the use of AC nanowire sensing that can capture both magnitude and phase information of the device response (31.2); 31.3 is a review of “MEMS for Cell Mechanobiology” (Stanford U); and 31.4 is also a review, of “Organic Electrochemical Transistors for BioMEMS Applications”, from Ecole Nationale Supérieure des Mines.

U Cincinnati (et al.) follows, with a tempting look at a “novel multimodality lab-on-a-tube smart catheter”, which can accurately track multiple parameters in an injured brain (31.5); 31.6 (Ritsumeikan U) shows off another medical device, an all polymer pneumatic balloon actuator, fabricated from polymers such as polyimide and polydimethylsiloxane that we are familiar with in the chip business. Paper 31.7 from MC10 completes the session by demonstrating examples of skin-based systems that incorporate physiological sensors and actuators configured in stretchable formats.

After the morning sessions, the IEDM Entrepreneurs Lunch is back for a third year, featuring a presentation by Kathryn Kranen, Former President and CEO of Jasper Design Automation.

Also at lunchtime ASM is hosting their regular IEDM seminar (Wednesday this year, instead of the Monday as of last year) on “14nm & Beyond – Fins all Around”, at the Nikko Hotel across the street from the Hilton. There’s no website, so interested parties should contact Rosanne de Vries, by replying to [email protected]. And there’s a bit of self-promotion here, since I’m one of the guest speakers!

We are back to Process and Manufacturing Technology in S32 after lunch, with a focus on Advanced Process Modules. IBM details some of its work on finFETs formed by Directed Self Assembly (DSA) in 32.1, achieving 29 nm fin pitch, and maybe giving us more evidence that EUV may never happen..

In 32.2 Samsung discusses their 10-nm interconnect strategy; judging by the abstract, we might be moving to Cu+Ru liner by the time we get to 10 nm. An imec/Micron/Hynix joint paper (32.3) reveals a new front-end scheme (gate and diffusion replacement), which allows high-thermal budget processes for applications such as control logic for memory (e.g. DRAM periphery).

Paper 32.4 is from Albany CNSE and its sponsors, examining the contact resistivity on n+ InGaAs fin sidewall surfaces; U Tokyo discusses oxygen effects in Ge MOSFETs in 32.5; 32.6 is a review of ion implantation techniques and capabilities by Applied Materials, from doping to materials engineering; and 32.7 covers “A Novel Junctionless FinFET Structure with Sub-5nm Shell Doping Profile by Molecular Monolayer Doping and Microwave Annealing”. The lead authors are from National Nano Device Laboratories, National Chiao Tung U, and National Cheng Kung U, but Michael Current and Evans Analytical are also involved, so at the least there should be some interesting analytical data included.

Session 33 has Exploratory Devices as the subject, inevitably academic in nature – Carnegie Mellon starts off (33.1) showing a four-terminal spintronic device, followed by Tohoku U, investigating 1x-nm perpendicular-anisotropy CoFeB-MgO based MTJs (33.2). Then we have a two-sided graphene oxide doped silicon oxide based RRAM (33.3) from National Sun Yat-Sen U, Peking U, and Stanford U; and a new material raises its head in (33.4) – iodostannane, basically tin activated with iodine, in a new kind of transistor, the topological-insulator field-effect transistor.

National Nano Device Laboratories, et al., present CMOS-compatible Mo-disulphide 3DFETs in 33.5, and Stanford U end the session with a review of carbon nanotube transistors.

Reliability: BTI, HCI and Breakdown are dealt with in session 34. A SMIC-sponsored work on NBTI in HKMG is covered in 34.1, co-authored by Peking U, Liverpool John Moores U, and UCal Berkeley. Liverpool John Moores U and imec look at NBTI of Ge pMOSFETs (34.2), and AIST has researched PBTI in n-fin-TFETs in 34.3; imec is back in 34.4, reviewing BTI reliability in “beyond-silicon devices”; and 34.5 covers RTN in both SiON and HKMG devices, by Peking U and SMIC.

Samsung (34.6) studies hot carrier induced dynamic variation in nano-scaled SiON/Poly, HK/MG and finFET devices, and the final paper of the session is from IBM and SRDC, discussing breakdown mechanisms in dielectric BEOL stacks (34.7).

The last session (numerically), session 35, covers Compact Modeling of devices. MIT and Purdue U get together to present a new model for FETs, which uses only a few physical parameters and is consistent with the virtual source model (35.1). They demonstrate its accuracy by comparison with measured data for III-V HEMTs and ETSOI Si MOSFETs.

NXP/UFRGS have a new noise (RTN/LFN) model for MOSFETS in 35.2, followed by IBM discussing several width dependent transistor current characteristics (35.3). We jump to TSVs in 35.4, with a CEA-Leti (et al.) study of thermal dissipation in 3D ICs and an associated model; IMECAS presents a surface potential-based compact model for a-IGZO TFTs in RFID applications in 35.5; and Purdue U/GLOBALFOUNDRIES model MTJs in 35.6.

Chronologically the last papers are due at 4.05 pm – by then a lot of attendees will have headed for home, especially since this year’s conference is so close to the Christmas break.

I will definitely be suffering from information overload and becoming brain-numb, but with 218 papers and an average of six parallel sessions at any one time, plus the offsite events, that’s not really surprising. On the other hand, where else do we go to get all this amazing stuff?

Time to unwind, maybe do a little holiday shopping, and go for an indulgent meal.

References:

[1] H.J. Yoo et al., “Demonstration of a reliable high-performance and yielding Air gap interconnect process”, IITC 2010, pp. 1-3

[2] J. Jang, et al., “Vertical Cell Array using TCAT (Terabit Cell Array Transistor) Technology for Ultra High density NAND Flash Memory” VLSI 2009, pp.192-193

[3] M. G. Farooq et al., “3D Copper TSV Integration, Testing and Reliability”, IEDM 2011, pp.143-146