Next week, the researchers and practitioners of the electron device world will be gathering in Washington D.C. for the 2013 IEEE International Electron Devices Meeting. To quote the conference web front page, “IEDM is the flagship conference for nanometer-scale CMOS transistor technology, advanced memory, displays, sensors, MEMS devices, novel quantum and nano-scale devices and phenomenology, optoelectronics, devices for power and energy harvesting, high-speed devices, as well as process technology and device modeling and simulation. The conference scope not only encompasses devices in silicon, compound and organic semiconductors, but also in emerging material systems.”

From my perspective at Chipworks, focused on chips that have made it to production, it’s the conference where companies strut their technology, and post some of the research that may make it into real product in the next few years.

In the last few days I’ve gone through the advance program, and here’s my pick of what I want to try and get to, in more or less chronological order. As usual there are overlapping sessions with interesting papers in parallel slots, but we’ll take the decision as to which to attend on the conference floor.

For the second year the conference starts on the Saturday afternoon, with a set of six 90-minute tutorials on a range of leading-edge topics:

- Nano Electronics – The use of Low-Dimensional Systems for Device Applications, Joerg Appenzeller,Purdue University

- Interface Properties for SiC and GaN MOS Devices, T. Paul Chow, Rensselaer Polytechnic Institute

- Energy Harvesting for Self-Powered Electronic Systems, Rob van Schaijk R&D Manager Sensors &Energy Harvesters, Holst Centre / IMEC

- Tunnel FETs – Beating the 60 mV/Decade Limit, Erik Lind, EIT, Lund University

- Atomic-Scale Modeling and Simulations for Nanoelectronics, Sumeet C. Pandey and Roy Meade,Emerging Memory Group, Process R&D, Micron Technology Inc.

- 3D Chip Stacking, Mukta Farooq, Systems & Technology Group, IBM

The first three are from 2.45 – 4.15, and the remainder from 4.30 – 6.00. I won’t make it to any of them; dedicated nerd I may be, but I want at least some of my weekend!

On Sunday December 4th, we start with the short courses, “Challenges of 10nm and 7nm CMOS Technologies” and “Beyond CMOS: Emerging Materials and Devices.”

Aaron Thean of IMEC has organised the former, and we have some impressive speakers – Frederic Boeuf, ST Microelectronics, (Device Challenges and Opportunities for 10nm and Below CMOS Nodes), Zsolt Tokei, also of IMEC, (Challenges of 10nm & 7nm Advanced Interconnect), Andy Wei, GLOBALFOUNDRIES, (Process Integration Challenges in 10nm CMOS Technology), Paul Franzon, NCSU, (Manufacturing, Design, and Test of 2.5D- and 3D-Stacked ICs), and Mark Neisser, Sematech (Lithography Challenges and EUV Readiness for 10nm and Beyond). With 14-nm product expected to hit the market next year, we need to look ahead, so this is appropriate – on the Intel clock, 10-nm is only two – three years away!

I’m now telling folks to think about the end of silicon, at least as we know it, since my brain will not wrap around the idea of 10- and 7-nm gates, and 10-nm gates are only 30 – 40 atoms across, depending on orientation! There’s lots of talk about integrating high-mobility materials onto silicon (imec had an announcement about InGaAs finFETs only a few weeks ago), so this course will help put that into context and cover off how the transistors fit into the rest of the stack.

Tom Theis of SRC has set up the other short course; now that we are reaching the end of silicon transistors, where do we go beyond CMOS?

Ken Uchida of Keio University reprises some of the first course with a session on Extending the FET; then Adrian M. Ionescu from the Ecole Polytechnique Federale de Lausanne discusses Tunnel FETs to give insights into perhaps the best known low-voltage device.

Nanomagnetic Devices are reviewed by Rolf Allenspach from IBM Zurich Research Labs, looking at the material properties and challenges, and some example devices.

All of these futuristic devices have to be compared to each other to see which ones have practical potential, so Dmitri Nikonov of Intel covers off Performance Benchmarking Methodology for Emerging Devices, looking at the rigorous methodology developed by the SRC’s Nanoelectronics Research Initiative, with some comparative results.

The final talk is on Emerging Devices for Quantum Computing by Michelle Simmons from the University of New South Wales, showing the device requirements for a practical quantum computer, then a quick survey of exploratory devices, and a closer look at one or two promising device concepts.

So some good solid stuff – although the courses make a long Sunday, from 9 a.m. to 5.30 p.m., but it’s worth sticking around to the end.

For the first time I can remember the Sunday evening has some extra sessions; Sematech is hosting a session on “Beyond CMOS” at the Fairfax at Embassy Row, from 5:30 – 8:35; and Leti will host a workshop on “Latest Advances in Cost-effective and Power-efficient Technologies for the Future of the Semiconductor Industry” from 6 – 9 pm at the Churchill Hotel, across the street from the Hilton.

Monday morning we have the plenary session, with three pertinent talks on the challenges of contemporary electronics:

- Graphene Future Emerging Technology, by Andrea Ferrari, from the University of Cambridge – given the developments in this field in the last few years, it’s time to look ahead and try and create a roadmap for this potentially disruptive technology, so this should be illuminating;

- Heterogeneous 3D Integration – Technology Enabler Toward Future Super-Chips, Mitsumasa Koyanagi, Tohoku University – we are already seeing a form of heterogeneous integration in RF front-end modules (but at the package level), and with Luxtera’s optical interface chips, but this talk will describe the higher levels of integration being researched at Tohoku U and elsewhere.

- Smart Mobile SoC Driving the Semiconductor Industry: Technology Trend, Challenges and Opportunities, Geoffrey Yeap, Qualcomm. As VP of Technology, Geoffrey Yeap has been at the heart of the mobile revolution, and helped push the company into the top ten; so this should be an interesting review of the last few years of mobile chip developments, and the challenges of squeezing more and more functionality onto ICs, for more and more RF bands, and in ever thinner phones.

At lunchtime ASM is hosting their regular IEDM seminar (Monday this year, instead of the Wednesday as in previous years) on Integrating High Mobility Materials, again at the Churchill Hotel.

After lunch we have seven parallel sessions coming up! Session 2 gets straight into the way-ahead material with papers on germanium & III-V CMOS devices, although we seem to be moving away from R towards D in the R&D spectrum; for example, paper 2.8 from IBM builds InGaAs n- and SiGe p-MOSFETs on hybrid substrates formed by direct wafer bonding of SiGe and InGaAs layers.

Session 3 details MRAM and NAND flash memories, starting with an invited talk by AIST on Future Prospects of MRAM Technologies (3.1), and the session ends with papers from Hynix and Macronix, the former on a 1x-nm multi-level cell NAND flash (3.6), and the latter on a dual-channel 3D NAND flash (3.7).

In session 4, we have the more futuristic topic of Steep Slope Devices, including papers from imec (4.2) and Intel (4.3) on tunnel FETs.

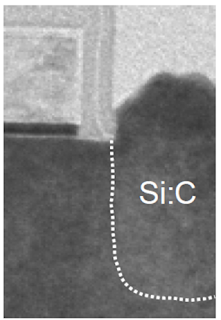

Now that we are into the finFET era, there is an interesting simulation paper in session 5; Analysis of Dopant Diffusion and Defects in Fin Structure (5.7), a joint paper by Panasonic and imec.

Session 6 focuses on Power Devices, with an indication that TSMC is getting into the business; they have a joint paper with Honk Kong UST on interface traps in Al2O3/AlGaN/GaN MIS devices (6.3). Mitsubishi is giving an invited talk on high voltage and large current SiC power devices (6.5), and we get back to MOS with a joint paper on the operating limits of LDMOS from NXP and U Twente.

The first two papers in session 7 discuss the reliability degradation caused by TSVs and 3D stacking, as measured by DRAM retention time; it appears that if wafers are thinned to 30 microns or less the DRAM performance drops off significantly due to stresses caused by the TSVs and microbumps (7.1, 7.2).

This year’s IEDM has focus sessions, and session 8 is the first, on Sensors and Microsystems for Biomedical Applications, with seven invited talks on different aspects of biosensors and biomedical devices.

Then in the evening we have the conference reception at 6:30, through until 8 pm.

Tuesday morning we have another seven parallel sessions, starting with session 9 on Advanced CMOS Technology, so one I will definitely be targeting. The first paper (9.1) is TSMC’s launch of their 16-nm finFET process, with a claimed doubling of logic density over their 28-nm process, with more than 35% speed gain or over 55% power reduction, and a 0.07 sq. micron 6T SRAM cell size.

|

|

Comparison of TSMC 16-nm finFET performance with 28-nm HKMG planar process (Source: TSMC, IEDM)

|

That is followed (9.2) by the competing 20-nm FDSOI process from the ISDA Alliance (IBM, STMicroelectronics, Renesas, GLOBALFOUNDRIES, SOITEC, and CEA-LETI).

Paper 9.3 takes us into the world of 3D-IC with a paper on layered ultrathin-body (UTB) circuits stacked on 300nm-thick interlayer dielectric (ILD) layers.

|

|

TEM image of 3D-layered UTB chip (Source: NNDL/Stanford/NTHU/UC Berkely, IEDM)

|

Amorphous silicon layers were deposited and crystallized with laser pulses, then planarized with low-temperature CMP to thin the layers, allowing formation of ultrathin, ultraflat devices.

IBM takes the next slot (9.4) with what looks like an update on their 22-nm gate-first process debuted last year (paper 3.3 last year), discussing 2nd Generation Dual-Channel Optimization with cSiGe for 22nm HP Technology and Beyond.

Intel also gives an update, this time on their eDRAM technology disclosed at the VLSI Symposium in June (Retention Time Optimization for eDRAM in 22nm Tri-Gate CMOS Technology, 9.5).

|

|

Details from Intel eDRAM paper at 2013 VLSI Technology Symposium

|

The session finishes up with a paper on embedded flash in a 55nm process from Fujitsu (9.6), and one on SRAM-like local interconnect structures for 20nm middle-of-line metallization from GLOBALFOUNDRIES; they claim that this helps them “achieve industry’s most optimum 20nm technology offerings.”

So I guess from the above I will be in session 9 all morning, so I will have to give session 10 on RRAM and FERAM a miss, even though there is interesting progress in the field, including 28nm RRAM in a paper (10.3) co-authored by TSMC.

Session 11 is focused on Flexible Electronics, a look into the future, but not too far away, judging by some of the talks.

Session 12 is the first on Modeling and Simulation, focusing on Technology CAD, with a few topics that catch my eye; paper 12.2 on Alloy Scattering in SiGe Channel from Samsung; Mobility in High-K Metal Gate UTBB-FDSOI Devices, an invited talk (12.5) from STMicroelectronics; Threshold Behavior of the Drift Region: the Missing Piece in LDMOS Modeling (12.7), from NXP; and Copper Through Silicon Via Induced Keep Out Zone for 10nm Node Bulk FinFET CMOS Technology (12.8), a joint paper from imec and Synopsys.

It seems that session 13 is a bit of a catch-all session on Advanced Manufacturing, since it includes invited papers on 3D memory (13.1) from Micron, GaN-on-Si from Toshiba (13.2), photonics on SOI by Luxtera and STMicroelectronics (13.3), TSMC’s take on glass interposers (13.4) and 450mm (13.7), and III-V growth on 300mm wafers from Aixtron (13.6).

Next we have another bio-session, BioMEMS and BioSensors, including two DNA analysis-on-chip papers (14.1 & 14.3). The last parallel session of the morning is session 15, on Reliability of BEOL and FEOL Devices, and it now seems that graphene and nanotubes have been around long enough that we have an invited talk on their reliability (15.1).

The speaker at the conference lunch will be David Luebke, Senior Director of Research at Nvidia, on the topic, The Current State-of-the-Art and Advances in Visual/GPU Computing.

Session 16 in the afternoon is about III-V Logic, looking ahead to when silicon can no longer provide the performance needed.

Session 17 is another focus session, this time on Analog and Mixed Signal Circuit/Device Interactions. We have a series of invited talks on the impact of nanometer scaling and finFETS on analog design and performance, RF technology, and a look at terahertz RF in CMOS, all of which catch my interest.

We are back to Sensors, Resonators, and Microsystems in session 18, and Nanosheet and Nanotube Technology in session 19, and it seems that molybdenum disulphide is now taking attention away from graphene since there are a couple of papers on that topic.

Session 20 is another multi-topic group of papers, on Fully Depleted Planar, 3D Ge Device Technology and RRAM Memory processing. We have TSMC and GloFo/Samsung/imec talking Ge finFETs (20.1 & 20.4), Si nanowires from IBM (20.2), and gate-last FDSOI from STMicroelectronics and CEA-LETI (20.3); two papers on doping finFETS by AIST/Nissin and AMAT/GloFo/Hynix (20.5 & 20.6); and to finish the session two RRAM talks by Macronix/National TsingHua U and Stanford U (20.7 & 20.8). The last paper uses block copolymer self-assembly lithography to get the device down to less than 12nm.

Memory Characterization and Reliability is the subject of Session 21, mostly of resistive memories; Session 22 is another Modeling and Simulation group of papers, this time on Innovative Devices, mainly resistive memories.

That brings us to the end of the afternoon, and now we have a dilemma – three offsite events – IEDM is getting popular with the industry! Applied Materials is hosting a panel on “3D NAND Is a Reality – What’s Next?” at the Omni Shoreham Hotel from 5 – 7.30 pm; Coventor is also hosting a panel at the Churchill Hotel, from 5:30 – 8:30, on “Insights from the Experts on Advanced Technology Development”; and Synopsys is having a TCAD reception, again at the Churchill, from 6 – 8 pm.

Once we’re sated from the hospitality, we can wander back to the Hilton and try and stay awake for the conference evening panels:

“Is there life beyond conventional CMOS?” moderated by Jeff Welser of IBM – now becoming a perennial question! The panelists are An Chen (GLOBALFOUNDRIES), Tetsuo Endoh (Tohoku University), Marc Heyns (IMEC Fellow), Mark Rodwell (UC Santa Barbara), Alan Seabaugh (Notre Dame), and Ian Young (Intel).

And:

“Will Voltage Scaling in CMOS Technology Come to an END?” with Kevin Zhang of Intel as moderator. Panelists for this session are Rob Aitken (ARM), Kelin Kuhn (Intel), Sreedhar Natarajan (TSMC), Tak Ning (IBM), Ann Steegen (imec), and Nobuyuki Sugii ( LEAP).

Wednesday morning has sessions 25 – 30; S25 on Advanced 3D Packaging and Emerging Memory Systems; TSMC is detailing an Array Antenna Integrated Fan-out Wafer Level Packaging (25.1), and Maxim is giving an invited talk on 3D Heterogeneous Integration for Analog, as the first two papers.

S26 covers Ge Channel and Nanowire Devices, obviously looking ahead, but catching my interest are A Group IV Solution for 7nm FinFET CMOS (26.3), from Synopsys/Stanford, and A Practical Si Nanowire Technology… (26.5) from Samsung.

Session 27 – Display and Imaging Devices has three papers on thin-film transistors for displays, and three imaging talks; Sony describes a Three-dimensional .. 1.20 μm Pixel Back-Illuminated CMOS Image Sensor (27.4), and Infineon has a novel Trench Gate Photo Cell (27.6) which could find use as the ambient light sensor that we see in so many mobile phones.

We have more III-V and TFET papers in session 28, but including an invited talk from Raydeon (More than Moore: III-V Devices and Si CMOS Get It Together – 28.5) on integrating III-V devices with Si CMOS on a common silicon substrate, which should be interesting in these days of 3D.

Session 29 has a couple of interesting papers on BEOL from Renesas and Samsung (29.1 & 29.2), and Hitachi/ASET discusses Fabricating 3D Integrated CMOS Devices by Using Wafer Stacking and Via-last TSV Technologies (29.5).

Conductive Bridge and Phase Change RAM papers make up session 30; the first two are CBRAM, and the rest PCM. Micron discusses Interface Engineering for Thermal Disturb Immune Phase Change Memory Technology in paper 30.4.

After the morning sessions, the IEDM Entrepreneurs Lunch is back for a second year, with Steve Nasiri, founder of Invensense, and now angel investor and mentor at Nasiri Ventures LLC, as guest speaker.

We are back to Characterization, Reliability, and Yield in S31 after lunch, with a focus on Device Variation and Noise. STMicroelectronics is giving an invited presentation on the Growing Impact of Atmospheric Radiations on sub-65nm CMOS BULK/FDSOI Technologies (31.1), we have two papers on SRAM, and the last three discuss random telegraph noise in MOSFETs, resistive RAM, and HEMTs, respectively.

Session 32 is the third Modeling and Simulation session, this time on Modeling Beyond CMOS Devices, Interconnects and GaN HEMT – getting a bit esoteric for my focus, unfortunately – but then with all the parallel sessions we have to miss some of them.

The last session (numerically), session 33, covers Circuit/Device Variability and Reliability. Asen Asenov of University of Glasgow/Gold Standard Simulations has a joint paper with IBM on Simulation Based Transistor-SRAM Co-Design in the Presence of Statistical Variability and Reliability (33.1), detailing the impact of process and statistical variability and reliability on SRAM cell design in 14nm technology node SOI FinFET transistors; with Intel’s 14nm due next year we might get some insights, though time will tell if they have moved to SOI trigate transistors from the bulk material that they currently use at 22nm.

By the end, I’m usually suffering from information overload and becoming brain-numb, but with 215 papers and an average of six parallel sessions at any one time, plus the offsite events, that’s not really surprising. On the other hand, where else do we go to get all this amazing stuff?